ГОСТ Р 71269-2024

НАЦИОНАЛЬНЫЙ СТАНДАРТ РОССИЙСКОЙ ФЕДЕРАЦИИ

Системы автоматизированного проектирования электроники

ТИПОВОЙ МАРШРУТ ПРОЕКТИРОВАНИЯ И МОДЕЛИРОВАНИЯ АНАЛОГОВЫХ И СМЕШАННЫХ ЦИФРО-АНАЛОГОВЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ

Electronics automated design systems. Design flow for design and simulation of analog and mixed electronic circuits

ОКС 31.020

29.100.01

Дата введения 2024-04-01

Предисловие

1 РАЗРАБОТАН Обществом с ограниченной ответственностью "Научно-исследовательский институт "АСОНИКА" (ООО "НИИ "АСОНИКА"), Обществом с ограниченной ответственностью "Платформ" (ООО "Платформ") и Обществом с ограниченной ответственностью "ПСБ Софтвер" (ООО "ПСБ Софтвер")

2 ВНЕСЕН Техническим комитетом по стандартизации ТК 165 "Системы автоматизированного проектирования электроники"

3 УТВЕРЖДЕН И ВВЕДЕН В ДЕЙСТВИЕ Приказом Федерального агентства по техническому регулированию и метрологии от 29 февраля 2024 г. № 269-ст

4 ВВЕДЕН ВПЕРВЫЕ

Правила применения настоящего стандарта установлены в статье 26 Федерального закона от 29 июня 2015 г. № 162-ФЗ "О стандартизации в Российской Федерации". Информация об изменениях к настоящему стандарту публикуется в ежегодном (по состоянию на 1 января текущего года) информационном указателе "Национальные стандарты", а официальный текст изменений и поправок - в ежемесячном информационном указателе "Национальные стандарты". В случае пересмотра (замены) или отмены настоящего стандарта соответствующее уведомление будет опубликовано в ближайшем выпуске ежемесячного информационного указателя "Национальные стандарты". Соответствующая информация, уведомление и тексты размещаются также в информационной системе общего пользования - на официальном сайте Федерального агентства по техническому регулированию и метрологии в сети Интернет (www.rst.gov.ru)

Введение

Причиной разработки стандарта является необходимость стандартизации процесса моделирования аналоговых и смешанных цифро-аналоговых электрических схем, входящих в состав проектируемой электронной аппаратуры (ЭА).

Стандарт распространяется на маршрут моделирования электрических схем, то есть проведение виртуальных испытаний схемы и подсхемы, процедур оптимизации, выбор оптимального схемотехнического решения, с применением автоматизированных систем проектирования и виртуального моделирования электрических схем. Его цель - автоматизация разработки электрических принципиальных схем, с применением математического моделирования, и снижение затрат на разработку, производство и обслуживание ЭА за счет повышения качества разработок и скорости проектирования.

1 Область применения

1.1 Настоящий стандарт предназначен для применения предприятиями промышленности и организациями при использовании электронных систем проектирования и моделирования виртуальных двойников электронных узлов (ЭУ) на ранних этапах проектирования, изготовления и испытаний ЭУ.

1.2 Системы проектирования и моделирования электрических схем применяются при проектировании ЭА и электронной компонентной базы (ЭКБ) следующего назначения: для оборонно-промышленного комплекса, для аэрокосмической отрасли, для судостроения, медицины, автомобильной отрасли, для навигации и радиолокации, потребительской отрасли, для связи (телекоммуникации), для систем безопасности, для автоматизированного транспорта и движущейся робототехники.

1.3 Виртуальное моделирование электроники не может полностью заменить натурные испытания, однако может дополнить их и позволить получить данные, которые сложно и иногда даже невозможно получить методом натурных испытаний.

1.4 Виртуальные испытания электроники проводят:

- на ранних этапах проектирования (до изготовления опытного образца);

- после изготовления и натурных испытаний опытного образца для проверки работоспособности ЭА и ЭКБ в условиях ВВФ, в том числе в критических режимах, которые не могут быть воспроизведены с помощью натурных испытаний.

1.5 Крайне важной характеристикой при выборе САПР для проектирования и автоматизированного моделирования электрических схем является возможность и качество ее интеграции с другими применяемыми в организации САПР, в первую очередь с САПР ПП.

1.6 Настоящий стандарт базируется на [1].

2 Нормативные ссылки

В настоящем стандарте использованы нормативные ссылки на следующие стандарты:

ГОСТ Р 70201 Системы автоматизированного проектирования электроники. Оптимальное сочетание натурных и виртуальных испытаний электроники на надежность и внешние воздействующие факторы. Требования и порядок проведения при выполнении технического задания на НИОКР

ГОСТ Р 70290 Системы автоматизированного проектирования электроники. Термины и определения

ГОСТ Р 70292 Системы автоматизированного проектирования электроники. Подсистема автоматизированного создания карт рабочих режимов электронной компонентной базы

Примечание - При пользовании настоящим стандартом целесообразно проверить действие ссылочных стандартов в информационной системе общего пользования на официальном сайте Федерального агентства по техническому регулированию и метрологии в сети Интернет или по ежегодному информационному указателю "Национальные стандарты", который опубликован по состоянию на 1 января текущего года, и по выпускам ежемесячного информационного указателя "Национальные стандарты" за текущий год. Если заменен ссылочный стандарт, на который дана недатированная ссылка, то рекомендуется использовать действующую версию этого стандарта с учетом всех внесенных в данную версию изменений. Если заменен ссылочный стандарт, на который дана датированная ссылка, то рекомендуется использовать версию этого стандарта с указанным выше годом утверждения (принятия). Если после утверждения настоящего стандарта в ссылочный стандарт, на который дана датированная ссылка, внесено изменение, затрагивающее положение, на которое дана ссылка, то это положение рекомендуется применять без учета данного изменения. Если ссылочный стандарт отменен без замены, то положение, в котором дана ссылка на него, рекомендуется применять в части, не затрагивающей эту ссылку.

3 Термины, определения и сокращения

3.1 В настоящем стандарте применены термины по ГОСТ Р 70290.

3.2 В настоящем стандарте использованы следующие сокращения:

ВВФ - внешние воздействующие факторы;

ВИ - виртуальные испытания;

ИС - интегральная схема;

КМОП - комплементарная структура металл - оксид - полупроводник;

КРР - карты рабочих режимов;

НТД - нормативно-техническая документация;

ПП - печатная плата;

САПР - система автоматизированного проектирования;

ТЗ - техническое задание;

ТТЛ - транзисторно-транзисторная логика;

УГО - условно-графическое обозначение;

ЭА - электронная аппаратура;

ЭУ - электронный узел, который может являться функциональной частью печатного узла, либо, наоборот, совокупность нескольких печатных узлов, объединенных единым функциональным назначением;

ЭКБ - электронная компонентная база;

ЭРИ - электрорадиоизделие;

ЭРЭ - электрорадиоэлемент.

4 Общие положения

4.1 Целью разработки настоящего стандарта является установление требований к автоматизированному процессу проектирования электрических схем, на основе создания виртуального двойника электрической схемы и проведения ВИ в соответствии с ГОСТ Р 70201.

Для достижения поставленной цели в стандарте устанавливаются следующие единые требования:

- к порядку и виду проводимых работ, в совокупности составляющих целостный унифицированный маршрут проектирования схемы;

- к составу виртуальных испытаний, по результатам которых выдается заключение о корректности проекта электрической схемы с точки зрения соответствия требованиям ТЗ в части потребления питания, функциональных параметров, частотных диапазонов, стабильности работы схемы и других параметров, связанных с функционированием электрической схемы в составе ЭА с учетом ВВФ и возможных отклонений номиналов ЭКБ.

4.2 Организация работ по применению систем автоматизированного проектирования и моделирования электрических схем

Использование тех или иных инструментов САПР может быть "точечным", программное обеспечение зачастую применяется разработчиками ситуативно, по мере необходимости. Однако рекомендуется следовать указаниям настоящего стандарта и выстроить в организации, разрабатывающей ЭА, унифицированный сквозной маршрут разработки на основе САПР моделирования аналоговых и смешанных электрических схем, позволяющий как использовать автоматизацию на всех этапах проектирования, так и войти в САПР "точечно" на любом из этапов, что дает возможность сократить затраты на разработку и ускорить выход на рынок.

5 Этапы проектирования и моделирования электрических схем

5.1 Ввод электрической принципиальной схемы

Первым этапом маршрута проектирования является ввод электрической принципиальной схемы отдельных узлов, трактов и/или системы в целом. Редактор для разработки схем в САПР должен позволять разбивать схему на отдельные страницы, составлять как плоские, так и иерархические схемы, а также предоставлять пользователю возможность редактировать (изменять и копировать) схемные элементы (УГО), создавать новые УГО, вести унифицированную библиотеку схемных элементов с возможностью параметрического поиска, а также назначать схемным элементам необходимые модели для дальнейшего проведения моделирования электрической схемы. Последующие этапы моделирования разработчик может выбирать и комбинировать в зависимости от функционального состава и назначения схемы, а также от предполагаемых условий эксплуатации. В зависимости от результатов моделирования тех или иных узлов схемы разработчик принимает соответствующие решения - о замене электронных компонентов, изменении номиналов или допусков или о корректировке электрической схемы в целом.

5.2 Подготовка "испытательных стендов" и "вариантов исполнения"

Для реализации данного этапа САПР моделирования должна позволять разработчику выделять отдельные части схемы и выполнять их моделирование в виде так называемых испытательных стендов, с заданием требуемых параметров моделей, и с подачей соответствующих напряжений источников питания и входных сигнальных или шумовых воздействий. Таким образом, разработчик получает возможность выполнять моделирование и анализ отдельных участков схемы, при этом не требуется копировать или переносить эти "подсхемы" в отдельный редактор, что снижает вероятность внесения ошибок и устраняет "человеческий фактор" на этапе моделирования.

5.3 Анализ точки смещения схемы

Одним из первых этапов моделирования является анализ напряжений и токов в различных цепях электрической схемы в установившемся режиме. На этом этапе можно определить и проверить напряжения смещения, например, на выводах транзисторов, токи покоя, и другие характеристики схемы. Анализ точки смещения учитывает любые источники напряжения, подаваемые на схему, и любые начальные условия, установленные для устройств или узлов в схеме (например, начальное напряжение на конденсаторе или начальное состояние цифрового вентиля). Результаты этого этапа используются многими дальнейшими этапами моделирования, поэтому САПР должна давать возможность не только отображать результаты моделирования на экране, но и сохранять их в виде файла для дальнейшего использования.

5.4 Анализ схемы по постоянному току

На этапе анализа по постоянному току вычисляют точку смещения схемы в диапазоне значений при варьировании номинала источника напряжения или тока, температуры, глобального параметра или параметра какой-либо модели. Варьируемое значение может увеличиваться в линейном или логарифмическом масштабе или представлять собой список возрастающих значений. На этом этапе разработчик получает более полную информацию о том, как функционирование схемы зависит от варьирования тех или иных параметров. Это полезно, например, если разработчик хочет увидеть реакцию схемы на изменение напряжения питания или посмотреть, как изменение номинала резистора влияет на реакцию схемы.

5.5 Анализ схемы по переменному току

Этот этап используется для расчета частотной и фазовой характеристик схемы путем варьирования частоты сигнала источника переменного тока, подключенного к схеме. Это линейный анализ, который вычисляет отклик схемы на слабый сигнал в заданном диапазоне частот, путем замены любых нелинейных моделей схемных устройств линейными моделями. Перед выполнением этого этапа выполняется анализ точки смещения по постоянному току, что используется для эффективной линеаризации схемы вокруг точки смещения. Следует отметить, что анализ переменного тока не позволяет учитывать такие нелинейные эффекты, как отсечение. Необходимо выполнить этап анализа переходных процессов, чтобы проанализировать и учесть такие эффекты.

5.6 Подготовка входных воздействий - стимулов

Перед проведением дальнейших испытаний схемы разработчик должен выполнить этап подготовки стимулирующих воздействий на схему. Для этой цели в САПР должны быть предусмотрены соответствующие параметризованные библиотеки типовых сигналов, а также редактор, позволяющий выполнить настройку и редактирование сигнальных воздействий, которые будут поданы на вход электрической схемы при моделировании ее работы.

5.7 Анализ переходных процессов схемы

На этом этапе выполняют расчет отклика схемы на входные воздействия за период времени, заданный пользователем. На схему подается питание и входные стимулирующие воздействия. Разработчик анализирует корректность работы схемы и ее отдельных узлов. Начальное состояние схемы основывается на результатах этапа анализа точки смещения. САПР моделирования должна позволять планировать изменение тех или иных параметров на протяжении процесса моделирования (например, может быть более эффективным уменьшить относительную точность моделирования с 0,001% до 0,1%, в периоды меньшей активности схемы, задав изменение точности каждую миллисекунду). Также САПР должна предоставлять возможность устанавливать контрольные точки в процессе моделирования. Пользователь может эффективно отмечать и сохранять состояние моделирования переходных процессов в контрольной точке и перезапускать моделирование переходных процессов с определенных контрольных точек. Это позволяет запускать симуляции в выбранные периоды. Это полезно, если у разработчика есть проблемы со сходимостью, поскольку можно запустить симуляцию с определенной контрольной точки, отмеченной во времени до ошибки симуляции, вместо того, чтобы запускать всю симуляцию с самого начала.

5.8 Варьирование параметров

Этап варьирования параметров, или параметрическая развертка, позволяет анализировать схему с изменением выбранного параметра в диапазоне значений и может выполняться при анализе переходных процессов, анализе по переменному или постоянному току. Параметры, которые САПР моделирования должна позволять изменять, включают источник напряжения или тока, температуру, какой-либо глобальный параметр или параметр определенной модели. Глобальный параметр обычно может представлять собой математическое выражение, а также переменную.

5.9 Создание моделей трансформаторов и анализ работы трансформаторов

САПР моделирования должна поддерживать моделирование линейных и нелинейных трансформаторов, создание и корректировку моделей, учет эффекта гистерезиса и др. Редактор моделей трансформаторов в САПР должен предоставлять возможность ввода кривой гистерезиса В-Н и других параметров модели. Этап выбора и ввода корректных моделей трансформаторов должен предшествовать этапам анализа схемы по переменному току и, в случае необходимости, анализа переходных процессов.

5.10 Анализ чувствительности схемы

Данный этап позволяет найти в схеме те компоненты, которые наиболее существенным образом влияют на функционирование схемы. Каждый компонент имеет допуск на свои характеристики, что в совокупности с неидеальными входными параметрами схемы дает большой диапазон возможных состояний и параметров на выходе схемы. Проанализировав чувствительность схемы, можно найти как наиболее критичные компоненты, сильнее всего влияющие на результат, так и второстепенные, допускающие большой разброс своих параметров. По результатам анализа разработчик получает информацию, в любом ли случае схема будет работать правильно, где следует поставить компоненты с меньшим допуском, а где можно сэкономить без вреда и обойтись более недорогим вариантом электронного компонента.

5.11 Подстройка и оптимизация схемы

На этапе подстройки схемы разработчик может автоматизированным способом изменить параметры компонентов, чтобы приблизить характеристики работы схемы к требуемым по техническому заданию. На этом этапе можно сделать подбор номиналов компонентов, учитывая требования к выходным параметрам схемы, представленные как численно, так и в виде кривых. Это удобно, когда под рукой не оказывается необходимых компонентов, а замена части из них влечет пересчет всех остальных.

5.12 Анализ работы схемы в разных режимах

Этот этап позволяет задать группу "измерений" на выходе и в узлах схемы, с целью получения характеристик работы схемы в различных режимах. Разработчик получает семейство графиков напряжений и токов и/или ряд измеренных значений. Например, после развертки (варьирования) для нескольких выходных значений источника напряжения, подключенного к схеме, может быть получена группа графиков для кривых заряда конденсатора. Анализ работы схемы с измерением значения времени нарастания в указанной точке создаст ряд значений времени нарастания, нанесенных на график в зависимости от варьирования напряжения источника. Разработчик на основании полученных данных делает выводы о работоспособности схемы в различных режимах.

5.13 Проверка на разброс номиналов

На данном этапе разработчик выполняет анализ, обратный подстройке схемы. Указывая список возможных номиналов компонентов, можно получить наборы графиков выходных параметров и убедиться, что в любом случае схема будет работать предсказуемо и в необходимых рамках.

5.14 Анализ надежности схемы

На данном этапе анализа схемы за отправную точку берутся допустимые условия работы для каждого компонента, их поведение при изменении температуры и необходимый запас по надежности. Результатом будет указание конкретных компонентов, которые могут отказать во время эксплуатации.

5.15 Статистический анализ схемы

Как правило, этот этап проводится с применением метода Монте-Карло, и позволяет выполнить анализ выхода годных изделий при заданной конфигурации схемы. Если условия таковы, что нет возможности спроектировать устройство, безотказно работающее в любом случае, можно провести анализ того, каким будет количество годных изделий при выпуске большой партии. Анализ Монте-Карло - это статистический анализ, который вычисляет отклик схемы, когда параметры модели случайным образом изменяются между заданными пределами допуска в соответствии с заданным статистическим распределением. Дискретные реальные компоненты, такие как резисторы, катушки индуктивности и конденсаторы, имеют определенный допуск, поэтому, например, резистор с номиналом 10 кОм и с допуском 1%, может иметь фактическое измеренное значение в интервале между 9900 и 10100 Ом (так как 1% от 10000 Ом соответствует разбросу в 100 Ом относительно номинала). Другие дискретные компоненты и полупроводники в цепи также будут иметь свои допуски, поэтому совокупный эффект допусков всех компонентов может привести к значительному отклонению от ожидаемой реакции схемы. Это особенно актуально для конструкций фильтров, где допуски применяемых компонентов могут привести к отклонению от требуемой характеристики фильтра. САПР моделирования должна предоставлять возможность выполнения статистического анализа с указанием как индивидуальных допусков, так и групповых допусков - для выбранных групп дискретных компонентов.

5.16 Анализ шума

Этап анализа шума выполняется таким же способом, как и анализ по переменному току, и позволяет вычислить выходной шум и эквивалентный входной шум в цепи. Выходной шум в указанном выходном узле представляет собой среднеквадратичную (RMS) сумму шума, создаваемого всеми резисторами и полупроводниками в цепи. Если схема считается бесшумной, то эквивалентный входной шум определяется как шум, необходимый на входе для создания такого же выходного шума. Это то же самое, что и деление выходного шума на коэффициент усиления схемы для получения эквивалентного шума. САПР моделирования должна предоставлять соответствующий инструментарий для анализа шума.

5.17 Температурный анализ

На данном этапе разработчик проверяет влияние изменения температуры на работу схемы. Изменение температуры может существенным образом повлиять на работу и характеристики схемы. Компоненты, наиболее подверженные изменению температуры, включают полупроводники, резисторы, конденсаторы и катушки индуктивности. Все эти компоненты в САПР моделирования должны иметь встроенный параметр модели температурной зависимости, так что выполнение развертки по температуре изменит компонент и последующее поведение схемы.

5.18 Анализ цифровых схем

На данном этапе, если это необходимо, разработчик проверяет работу цифровой логики в схеме с помощью САПР моделирования. САПР может использовать один и тот же механизм моделирования как для аналоговых, так и для цифровых частей, или это могут быть разные алгоритмы и принципы моделирования. Цифровые части ТТЛ и КМОП обычно моделируются как подсхемы и включают в себя общие цифровые функции, такие как вентили, регистры, триггеры, инверторы и т.д. В каждой подсхеме цифровой примитив САПР составляет функцию вентиля (И, ИЛИ и т.д.) и определяет синхронизацию и спецификацию интерфейса для функции вентиля. В случае совместного цифро-аналогового моделирования САПР должна предоставлять необходимые "соединительные" моделирующие элементы для симуляции взаимодействия между аналоговыми и цифровыми частями схемы.

5.19 Создание КРР ЭКБ - в соответствии с ГОСТ Р 70292.

5.19.1 Разработчики схем ЭА получают и передают все электрические характеристики, необходимые для КРР ЭКБ, работникам подразделения предприятия, на которое возложена обязанность выпуска КРР ЭКБ.

5.19.2 Работники подразделения предприятия, на которое возложена обязанность заполнения базы данных ЭКБ, регулярно для новой ЭКБ заносят в базу данных ЭКБ всю информацию, необходимую для создания КРР, содержащуюся в колонках "По НТД".

5.19.3 После проверки правильности применения ЭКБ в ЭА выводятся данные о результатах оценки номенклатуры, условий эксплуатации, электрических и температурных режимов работы ЭКБ. Эти данные в виде числовых значений параметров, характеризующих фактические и предписанные в НТД на ЭКБ условия их эксплуатации и режимы работы, оформляются в виде КРР. Традиционно в КРР пишется не ЭКБ, а ЭРИ.

Пример системы моделирования электрических схем - САПР PSpice A/D приведен в приложении А.

Пример системы создания КРР ЭКБ приведен в приложении Б.

Приложение А

(справочное)

Пример системы моделирования электрических схем - САПР PSpice A/D

Одним из самых популярных и мощных инструментов для проектирования и моделирования электрических схем заслуженно считается программный продукт PSpice A/D производства компании Cadence Design Systems [2]. Этот инструмент постоянно обновляется и имеет простой, доступный для понимания интерфейс.

Инструмент PSpice A/D является автоматизированной программной системой, позволяющей создать электрическую принципиальную схему и провести виртуальные испытания электрической схемы, а также выполнить при необходимости автоматизированную оптимизацию параметров схемы для достижения необходимых характеристик.

Симулятор цифро-аналоговых схем PSpice A/D совместно с опцией продвинутого анализа PSpice Advanced Analysis (АА) позволяет предсказать поведение изделия до его изготовления, что не только помогает исправить ошибки с меньшими потерями, но и провести улучшение схемы, быстро подобрав наиболее оптимальные компоненты.

PSpice позволяет компаниям сократить потери и расходы:

- время на диагностику и поиск неисправностей при испытаниях

- время на разработку следующей ревизии (косвенные потери)

- стоимость изготовления новой итерации прототипа (прямые затраты)

- время на правки из-за отказов при эксплуатации изделия

- время на инженерную работу вместо использования оптимизации

Конфигурация продуктов на базе PSpice:

PSpice A/D - симулятор схем на основе моделей SPICE;

PSpice Advanced Analysis - опция продвинутого анализа для PSpice;

OrCAD PSpice Designer (Capture + PSpice A/D) - схемный редактор и PSpice;

OrCAD PSpice Designer Plus (Capture + PSpice A/D + PSpice AA);

OrCAD PCB Designer Professional with PSpice - САПР OrCAD и PSpice.

Инструменты PSpice Advanced Analisys

Sensitivity (анализ чувствительности схемы):

Каждый компонент имеет допуск на свои характеристики, что в совокупности с неидеальными входными параметрами схемы дает большой диапазон возможных состояний и параметров на выходе схемы. Проанализировав чувствительность схемы, можно найти как наиболее критичные компоненты, сильнее всего влияющие на результат, так и второстепенные, допускающие большой разброс в своих свойствах. По результатам анализа выясняют, в любом ли случае схема будет работать правильно, где следует поставить компоненты с меньшим допуском, а где можно сэкономить без вреда и обойтись более недорогим вариантом.

Optimizer (подстройка схемы):

Можно сделать подбор номиналов компонентов, учитывая требования к выходным параметрам схемы, представленные как численно, так и в виде кривых. Это удобно, когда под рукой не оказывается необходимых компонентов, а замена части из них влечет перерасчет всех остальных.

Parametric Sweep (подбор номиналов):

Анализ, обратный подстройке схемы, в котором, указывая список возможных номиналов компонентов, можно получить наборы графиков выходных параметров и убедиться, что в любом случае схема будет работать предсказуемо и в необходимых рамках.

Smoke (анализ надежности схемы):

В этом анализе за отправную точку берут допустимые условия работы для каждого компонента, их поведение при изменении температуры и необходимый запас по надежности. Результатом будет указание конкретных компонентов, которые могут отказать во время эксплуатации.

Monte Carlo (анализ выхода годных изделий):

Если условия таковы, что нет возможности спроектировать устройство, безотказно работающее в любом случае, можно провести анализ того, каким будет количество годных изделий при выпуске большой партии. Может оказаться, что брак из-за случайного разброса параметров настолько маловероятен, что более тщательная проработка схемы и не требуется.

Уникальные возможности PSpice:

- интеграция PSPICE с MATLAB, что позволяет проводить совместные моделирования с применением инструментов обеих программ;

- возможность самостоятельного создания PSpice моделей на основе как данных производителя, так и графиков, полученных из практических измерений;

- настройка моделирования под управлением различных "событий", происходящих в схеме, с использованием контрольных точек для рестарта, продвинутых алгоритмов сходимости и "подстраивания" кривых;

- пополняющаяся библиотека из 33,000 готовых аналоговых и аналого-цифровых моделей, математических функций, и поведенческого моделирования.

Приложение Б

(справочное)

Пример системы создания карт рабочих режимов ЭКБ

Подсистема автоматизированного заполнения карт рабочих режимов ЭКБ "АСОНИКА-Р" является одной из 13 подсистем автоматизированной системы обеспечения надежности и качества аппаратуры "АСОНИКА" (https://asonika-online.ru/), предназначенной для анализа и обеспечения стойкости ЭА и ЭКБ к комплексным тепловым, механическим, электромагнитным воздействиям, усталостной прочности к тепломеханическим воздействиям, создания карт рабочих режимов ЭКБ, анализа показателей надежности ЭА и создания цифровых двойников ЭА и ЭКБ.

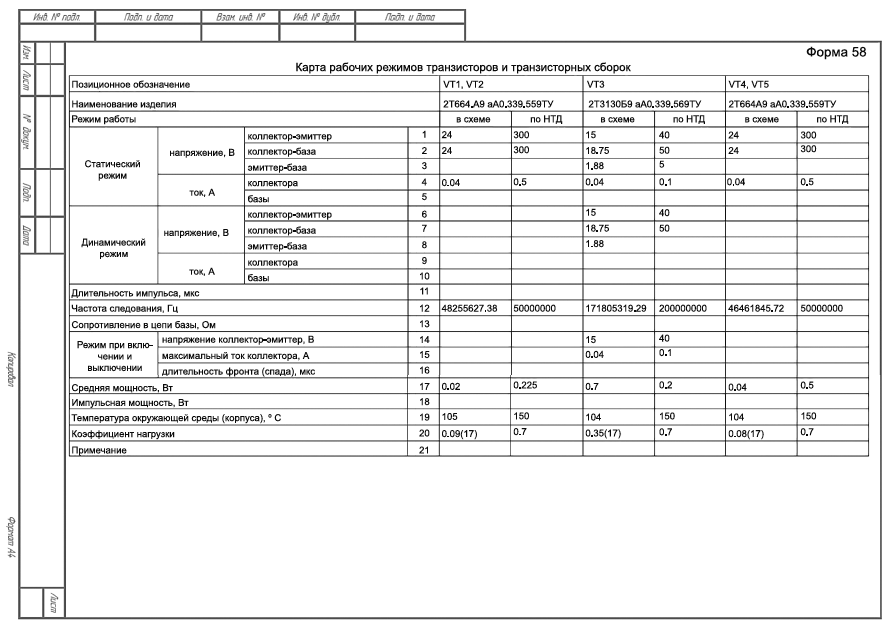

На рисунке Б.1 в качестве примера приведен фрагмент формы 58 КРР для транзисторов, созданной с помощью подсистемы "АСОНИКА-Р".

|

Рисунок Б.1 - Карта рабочих режимов (форма 58)

Библиография

[1] | Шалумов А.С. Дорожная карта развития "САПР электроники выше мирового уровня". - Ковров: ООО "НИИ "АСОНИКА", 2020. - 24 с.- Режим доступа: https://asonika-online.ru/news/432/ |

[2] | Фитцпатрик Д. Аналоговое проектирование и моделирование с использованием OrCAD Capture и PSpice. Второе издание |

УДК 621.865:8:007.52:006.354 | ОКС 31.020 29.100.01 |

Ключевые слова: система автоматизированного проектирования, программируемые, логические, интегральные схемы, маршрут проектирования, электронная аппаратура | |