ГОСТ Р 58286-2018

НАЦИОНАЛЬНЫЙ СТАНДАРТ РОССИЙСКОЙ ФЕДЕРАЦИИ

АРХИТЕКТУРА БАЗОВАЯ ПОСТРОЕНИЯ СИСТЕМ КОНТРОЛЬНО-ИЗМЕРИТЕЛЬНОЙ АППАРАТУРЫ AXIe-1

Технические требования

AXIe-1 base architecture for instrumentation

ОКС 35.200

Дата введения 2019-05-01

Предисловие

1 РАЗРАБОТАН Обществом с ограниченной ответственностью "VXI-Системы" (ООО "VXI-Системы")

2 ВНЕСЕН Техническим комитетом по стандартизации ТК 064 "Радиоэлектронные измерительные приборы"

3 УТВЕРЖДЕН И ВВЕДЕН В ДЕЙСТВИЕ Приказом Федерального агентства по техническому регулированию и метрологии от 23 ноября 2018 г. N 1031-ст

4 Настоящий стандарт разработан с учетом основных положений международного документа АХlе-1* "Технические требования к базовой архитектуре, редакция 3" (AXIe-1 "Base Architecture Specification, Revision 3", NEQ).

________________

* Доступ к международным и зарубежным документам, упомянутым в тексте, можно получить, обратившись в Службу поддержки пользователей. - .

Сопоставление содержания настоящего стандарта и примененного международного документа приведено в дополнительном приложении ДА

5 ВВЕДЕН ВПЕРВЫЕ

Правила применения настоящего стандарта установлены в статье 26 Федерального закона от 29 июня 2015 г. N 162-ФЗ "О стандартизации в Российской Федерации". Информация об изменениях к настоящему стандарту публикуется в ежегодном (по состоянию на 1 января текущего года) информационном указателе "Национальные стандарты", а официальный текст изменений и поправок - в ежемесячном информационном указателе "Национальные стандарты". В случае пересмотра (замены) или отмены настоящего стандарта соответствующее уведомление будет опубликовано в ближайшем выпуске ежемесячного информационного указателя "Национальные стандарты". Соответствующая информация, уведомление и тексты размещаются также в информационной системе общего пользования - на официальном сайте Федерального агентства по техническому регулированию и метрологии в сети Интернет (www.gost.ru)

Введение

Настоящий стандарт разработан на основе международного документа "АХlе-1. Технические требования к базовой архитектуре" ("АХlе-1: Base Architecture Specification, Revision 3"), разработанного компаниями международного консорциума AXIe. В настоящем стандарте приведена нумерация разделов, правил, разрешений и рекомендаций, соответствующая нумерации международного документа АХlе-1.

Настоящий стандарт устанавливает требования к разработке программно-аппаратных средств на основе архитектуры AXIe.

Настоящий стандарт содержит требования и разрешения, которые необходимо соблюдать при проектировании шасси AXIe и инструментальных модулей, а также устанавливает правила и порядок их механического, электрического и логического взаимодействия в рамках системы AXIe.

Базовая архитектура AXIe определяет расширяемую платформу для создания устройств общего назначения модульной контрольно-измерительной аппаратуры (КИА). Архитектура AXIe наследует лучшие черты более ранних платформ построения модульных систем в открытых стандартах VXIbus, PXI и LXI. Также как VXIbus и PXI, архитектура AXIe основана на популярной модульной вычислительной платформе с добавлением функциональности, необходимой разработчикам и пользователям КИА. Базовой платформой для архитектуры AXIe является платформа AdvancedTCA (АТСА) - открытая архитектура построения модульных вычислительных устройств, ориентированная на создание инфраструктуры коммуникационных систем. Архитектура АТСА содержит свод правил и положений, касающихся систем распределения питания, управления компонентами системы, взаимодействия по интерфейсам Ethernet и PCIe между модулями и другого функционала. Базовая архитектура AXIe имеет дополнительные возможности по сравнению с архитектурой АТСА, которые позволяют обеспечить синхронизацию по частоте, большой выбор триггерных сигналов для запуска процессов и организацию потоков данных между модулями, что крайне важно при реализации высокопроизводительных контрольно-измерительных систем.

Настоящий стандарт определяет набор механических, электрических и логических интерфейсов между модулями и шасси. Типичные шасси и модуль AXIe представлены на рисунке 1, упрощенная схема шасси - на рисунке 2. Модули AXIe устанавливают в слоты фронтального носителя модулей шасси и подключают к разъемам кросс-платы. Кросс-плата обеспечивает трассировку цепей питания и сигналов системного управления к инструментальным модулям, а также сигналов данных, частот и триггерных сигналов между инструментальными модулями. Менеджер шасси является выделенным контроллером управления системой, который отслеживает исправность подсистем шасси и модулей, управляет системой охлаждения и последовательностью включения питания шасси. В модулях могут быть реализованы любые функции, необходимые для проведения тестирования/измерений, например: измерение и анализ сигналов, формирование сигналов, ввод/вывод цифровых сигналов, организация потоков данных, компьютерные вычисления и многое другое.

Внешний ввод-вывод аналоговой и цифровой информации в системах АХlе-1 осуществляется через соединители, расположенные на фронтальных лицевых панелях модулей AXIe.

Кросс-плата AXIe поддерживает два стандарта интерфейсов последовательной передачи данных - LAN и PCIe. Оба интерфейса подходят для управления модулем и передачи данных измерений. Большинство модулей AXIe поддерживают один из этих интерфейсов, причем некоторые из них могут поддерживать оба интерфейса.

Интерфейс LAN лучше всего подходит для интеллектуальных модулей, поддерживающих программные интерфейсы высокоуровневых команд. Подобные модули AXIe, подключенные по интерфейсу LAN, должны удовлетворять требованиям стандарта LXI относительно протокола обмена и удобства использования программного обеспечения (ПО) в соответствии со стандартом AXIe-2.

Интерфейс PCIe лучше всего подходит для реализации в менее интеллектуальных модулях, которые управляются регистровыми командами низкого уровня. Такие модули PCIe работают как устройства расширения хост-компьютера и определяются в операционной системе хост-компьютера как стандартные периферийные устройства PCIe. Дополнительно эти модули должны соответствовать требованиям к ПО PXI согласно международной спецификации AXIe-2, в которой приведены требования к ПО архитектуры АХlе-1.

Таким образом, модели интеграции, программирования и использования модулей обоих типов уже знакомы большинству интеграторов систем тестирования и пользователям.

|

1 - модуль AXIe; 2 - шасси AXIe

Рисунок 1 - Шасси и модуль AXIe

|

Рисунок 2 - Схема шасси AXIe

Модули AXIe имеют высоту 320 мм, глубину 280 мм и ширину 30 мм. Каждый модуль обычно потребляет мощность от 100 до 200 Вт. Благодаря большой площади платы, внутреннему объему модуля и высокой мощности платформа AXIe подходит для построения систем, требующих большого числа каналов, высокой производительности измерений и/или эффективного использования пространства стойки.

Настоящий стандарт определяет базовую контрольно-измерительную платформу. Сопутствующие международные спецификации AXIe-3.n могут в дальнейшем определять дополнительные расширения к архитектуре AXIe-1, оптимизированные для определенных сегментов рынка. Например, спецификация AXIe-3.1 определяет расширение системы AXIe-1 для приложений тестирования полупроводниковых приборов.

Структура стандарта

Настоящий стандарт устанавливает набор правил, рекомендаций, разрешений и замечаний наряду с поясняющим текстом, таблицами и рисунками. С целью четкого определения требований настоящего стандарта в его тексте употребляются следующие ключевые слова:

- правило;

- рекомендация;

- разрешение;

- замечание.

Любой текст, не имеющий в качестве заголовков перечисленные ключевые слова, является описательной частью структуры системы или ее работы, изложенной в описательной или повествовательной форме.

Правила излагают основные требования настоящего стандарта, характеризующиеся словом "должно".

Соответствие данным правилам обеспечивает необходимый уровень совместимости оборудования различных производителей, ожидаемый системными интеграторами и конечными пользователями рынка КИА. Устройства, соответствующие настоящему стандарту, должны удовлетворять всем требованиям, изложенным в различных правилах.

Примечание - При нумерации правил первый символ указывает на раздел настоящего стандарта, следующее за ним число - на номер этого правила в определенном разделе.

Рекомендации обеспечивают дополнительное руководство, которое поможет производителям улучшить пользовательские характеристики устройств AXIe, характеризующиеся словом "следует". Следование рекомендациям улучшит функциональность, гибкость, совместимость и/или удобство использования устройств AXIe. Применение рекомендаций к устройствам не является обязательным.

Примечание - При нумерации рекомендаций первый символ указывает на раздел настоящего стандарта, следующее за ним число - на номер этой рекомендации в определенном разделе.

Разрешения подчеркивают гибкость настоящего стандарта и характеризуются словом "могут". Разрешения главным образом разъясняют диапазон решений проектирования, который доступен проектировщикам модулей и систем на их усмотрение. Они позволяют проектировщикам манипулировать функциональностью, стоимостью и другими факторами для создания изделий, отвечающих ожиданиям пользователей. Разрешения носят нейтральный характер и не предполагают их реализации.

Примечание - При нумерации разрешений первый символ указывает на раздел настоящего стандарта, следующее за ним число - на номер этого разрешения в определенном разделе.

Замечания подчеркивают некоторые важные нюансы настоящего стандарта. Они помогают лучше понять подтекст некоторых требований настоящего стандарта и/или выделить главное из частных требований. Замечания в основном содержат советы по проектированию.

Примечание - При нумерации замечаний первый символ указывает на раздел настоящего стандарта, следующее за ним число - на номер этого замечания в определенном разделе.

Все правила, рекомендации, разрешения и замечания должны рассматривать совместно с сопутствующим текстом, таблицами и рисунками. Правила могут явно или неявно содержать информацию, приведенную в тексте, таблицах и рисунках. Несмотря на то, что настоящий стандарт и предполагает, что все необходимые требования изложены в правилах, возможно, что некоторые важные моменты оговариваются в настоящем стандарте за пределами правил. С точки зрения максимальной совместимости со стандартом такие требования лучше трактовать как правила.

Настоящий стандарт основан на [1]. Правила, рекомендации, разрешения и замечания настоящего стандарта ссылаются на соответствующие требования [1]. Данные требования сопровождаются поясняющим контекстом (текстом, таблицами, рисунками и т.д.). Любые требования, которые не включены в правила, рекомендации, разрешения или замечания настоящего стандарта, исключают из требований к устройствам AXIe.

Успешная реализация устройств и систем AXIe требует знаний настоящего стандарта и [1].

Обзор архитектуры АТСА

Архитектура AXIe основана на ряде требований, предъявляемых к аппаратным и программным ресурсам, которые должны обеспечить простую интеграцию модулей и шасси AXIe разных производителей в мощную систему тестирования. За основу архитектуры AXIe взята архитектура АТСА, которая определяет модульную платформу, оптимизированную для телекоммуникационных приложений. AXIe добавляет к АТСА аппаратные и программные функции, необходимые для реализации систем КИА.

Архитектура АТСА дает определение открытой архитектуры модульных вычислительных устройств для построения высоконадежных сетей связи и телекоммуникационного оборудования. Основными механическими компонентами оборудования АТСА являются фронтальные платы и модули трассировки выводов зоны 3 фронтальных плат на заднюю стенку шасси - модули RTM, объединительная плата и носитель модулей. Фронтальные платы обеспечивают основную функциональность системы, в то время как платы RTM - возможность подключения к фронтальной плате с тыльной стороны крейта. Объединительная плата содержит соединители для подключения фронтальных плат, обеспечивая коммутацию сигналов и распределение питания. Носитель модулей - несущая конструкция для установки фронтальных плат и плат RTM. Одна объединительная плата и носитель модулей поддерживают подключение и установку не более 16 фронтальных плат и соответствующего числа плат RTM. На рисунке 3 приведена конструктивная связь между фронтальной платой, кросс-платой и платой RTM.

|

1 - фронтальная плата; 2 - зона 3; 3 - зона 2, 4 - зона 1; 5 - кросс-плата; 6 - плата RTM

Рисунок 3 - Фронтальная плата, кросс-плата и плата RTM

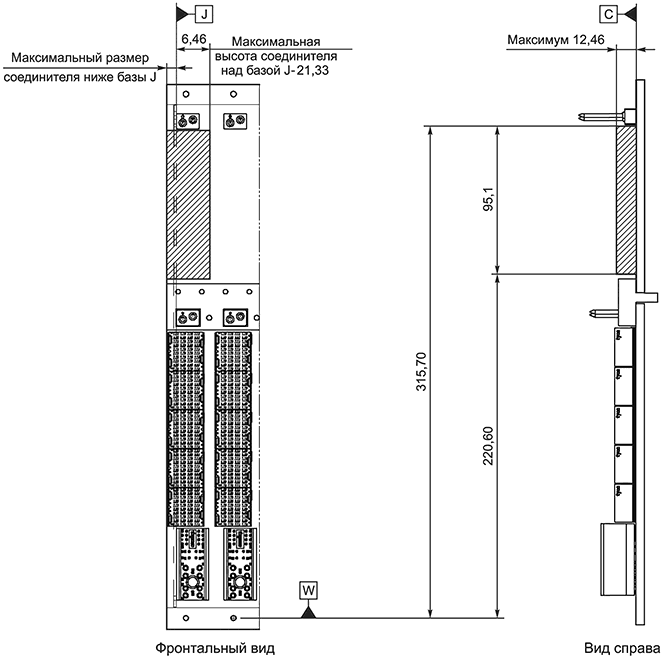

Фронтальная плата высотой 322,75 мм, шириной 30,48 мм и глубиной около 280 мм представлена на рисунке 4. Она имеет фронтальную лицевую панель с ручками для вставки и извлечения модуля. Область соединителей кросс-платы разделена на три зоны. Зона 1 содержит линии питания и линии для управления фронтальными платами. Зона 2 содержит линии передачи данных, сигналов синхронизации и триггерных сигналов. Зона 3 содержит линии ввода-вывода для платы RTM.

|

Рисунок 4 - Фронтальная плата ATCA

ATCA содержит разветвленную систему управления платформой, которая включает центральный менеджер шасси и распределенные контроллеры управления. Система отслеживает исправность, управляет питанием и охлаждением системы, контролирует совместимость соединений между модулями. Архитектура ATCA имеет уровень надежности 99,999%, поддерживаемый двойным резервированием критических ресурсов, "горячей заменой" плат и т.д.

Система спроектирована для работы от питания батарей напряжением минус 48 В. Питание распределяется между фронтальными платами с использованием дополнительных каналов питания.

ATCA содержит расширенные требования к характеристике охлаждения, что позволяет системным интеграторам создавать системы, в которых все компоненты имеют достаточное охлаждение.

Соединители зоны 2 содержат различные интерфейсы для обеспечения внутрисистемных коммуникаций между модулями. Для организации соединений Ethernet по схеме "двойная звезда" используют основной (base) интерфейсный канал. Другой интерфейсный канал (fabric) применяют для обмена по высокоскоростным последовательным интерфейсам передачи данных, в том числе по PCIe. Топология интерфейсного канала fabric обычно организована по схеме "двойная звезда". Две фронтальные платы с шасси служат концентраторами для каналов base и fabric, обеспечивая подключение ресурсов, необходимых для работы интерфейсов через эти каналы. Интерфейс fabric может иметь и иной вид топологии, например топологию полносвязной сети. В шасси также присутствуют каналы для передачи частот синхронизации, которые используются для маршрутизации телекоммуникационных тактовых частот через кросс-плату и интерфейс канала обновлений, обеспечивающий локальные соединения между совместимыми платами в пределах шасси. Все сигнальные линии в зоне 2 выполнены в виде дифференциальных пар.

Функции ATCA, включенные в AXIe

Архитектура AXIe содержит все конструктивные требования архитектуры ATCA, предъявляемые к сборкам фронтальных плат, соединителям зоны 1 и зоны 2 кросс-платы, самой кросс-плате и базовому блоку с некоторыми исключениями, касающимися необходимого количества слотов, поддержки плат RTM и требований к окружающей среде. В отличие от систем ATCA системы AXIe используют в лабораторных и производственных помещениях. Условия в них, как правило, отличаются от среды помещений телекоммуникационных аппаратных, в которых обычно применяется оборудование ATCA. Данные различия касаются систем подачи питания, диапазона температуры окружающей среды, диапазонов акустических воздействий, электромагнитной совместимости (ЭМС) и т.д. В целом каждый изготовитель оборудования AXIe несет ответственность за определение и указание подходящих требований к окружающей среде для устройств AXIe.

Архитектура AXIe включает большинство функций управления аппаратной платформой ATCA и требует от устройств и компонентов системы соблюдения всех требований архитектуры ATCA к управлению аппаратной платформой, за исключением нескольких требований, связанных с избыточностью (резервированием) и специфическими функциями для телекоммуникаций. Архитектура AXIe включает в себя расширение системы электронных ключей (electronic keying) для обеспечения уникальных функций и требований AXIe.

Архитектура AXIe поддерживает схему распределения питания ATCA для кросс-платы и фронтальных плат с исключениями, связанными с дублированием и диапазоном допустимых значений распределяемого напряжения. Аппаратура ATCA предназначена для приложений, рассчитанных на питание от внешних аккумуляторных батарей с напряжением минус 48 В. Изделия AXIe обычно применяют в тех местах, где основным источником питания служат локальные электрические сети переменного тока. Таким образом, типичные шасси AXIe должны содержать блок источника питания, который преобразует напряжение сети переменного тока в напряжение постоянного тока минус 48 В, распределяемого по кросс-плате AXIe.

Настоящий стандарт содержит требования к температуре для фронтальных плат и слотов фронтальных плат шасси ATCA. Однако обычные приложения AXIe не требуют избыточности в части систем охлаждения, которое предполагается в большинстве приложений ATCA.

В настоящем стандарте перечислены требования стандарта ATCA к интерфейсным портам base и fabric зоны 2 для кросс-платы и фронтальных плат с исключениями, связанными с избыточностью. Системы AXIe ограничены только одним видом топологии интерфейсных портов base (LAN) и fabric (PCIe) - "одиночная звезда".

Кроме того, в настоящем стандарте установлены требования к интерфейсу PCIe fabric, определенные в расширении PICMG 3.4 к [1]. Архитектура AXIe поддерживает не более 16 линий PCIe для каждого инструментального модуля.

Отличия архитектуры AXIe от архитектуры ATCA

Рынок общецелевой КИА не имеет требований к 99,999%-ному уровню надежности, предполагаемой на рынке телекоммуникационных систем. Поэтому архитектура AXIe не требует использования функций резервирования, определенных в [1]. Модули и системы могут выборочно реализовывать схемы дополнительного питания. Не требуется использование шины управления дополнительным питанием. На кросс-плате отсутствует трассировка линий каналов base и fabric ко второму концентратору системы.

Системы AXIe-1 не используют платы RTM. Сигналы ввода/вывода направляются через лицевые панели фронтальных модулей. Наличие в корпусах слотов RTM не обязательно. Последующие стандарты AXIe-3.n могут определять требования к сигналам зоны 3 кросс-платы или схемы модулей RTM для специализированных приложений рынка КИА. AXIe-1 определяет границы для модулей таким образом, чтобы они не пересекались с соединителями зоны 3 кросс-плат, соответствующих последующим стандартам AXIe-3.n.

Контрольно-измерительные устройства общецелевого назначения, как правило, предназначены для монтажа в стойки серии 482,6 мм. Это позволяет разместить в одном базовом блоке только 14 вертикальных слотов. Архитектура AXIe-1 допускает только 14 слотов вместо возможных 16 слотов в архитектуре ATCA.

Основной целью стандарта AXIe является обеспечение совместимости модулей, кросс-платы, базового блока и других компонентов системы с шасси. Источник питания, размеры, характеристики среды и другие нормативные требования к базовому блоку определяются каждым производителем шасси AXIe в соответствии с потребностями рынка.

Архитектура AXIe расширяет использование интерфейса частот синхронизации для дополнительных целей, сверх определенных в [1]. Кросс-платы AXIe поддерживают шинную топологию сигналов интерфейса частот синхронизации. Устройства AXIe, как и устройства ATCA, используют уровни MLVDS для линий. Однако шина использована модулями AXIe для синхронизации и транспортирования сигналов запуска общего назначения. Системы AXIe, как правило, не предоставляют специфических сигналов частоты синхронизации, определенных в [1] (опционально реализация этих требований допустима в архитектуре AXIe).

Архитектура AXIe не реализует интерфейс канала обновлений, как это определено в [1]. Освободившиеся контакты кросс-платы AXIe используют для организации одношинной топологии MLVDS для вновь введенных сигналов, подключаемых к контактам соединителя зоны 2. При этом устройства AXIe реализуют различные сигнальные схемы, определенные в настоящем стандарте. Устройства AXIe и компоненты системы поддерживают процедуру электронного ключа для предотвращения несовместимых соединений между устройствами AXIe и устройствами ATCA, установленными в одинаковую системную среду.

Новые возможности архитектуры AXIe относительно архитектуры ATCA

Архитектура AXIe предоставляет несколько новых функций, отсутствующих в архитектуре ATCA. Это накладывает дополнительные ограничения на совместное использование модулей и компонентов.

В настоящем стандарте вводится понятие "шина триггерных сигналов, TRIG[0-11]", которая состоит из 12 дифференциальных пар MLVDS для триггерных сигналов, проходящих через все слоты кросс-платы AXIe. Шина использует контакты соединителя зоны 2, которые используются в АТСА для канала обновлений, частот синхронизации и каналов fabric слотов 15 и 16.

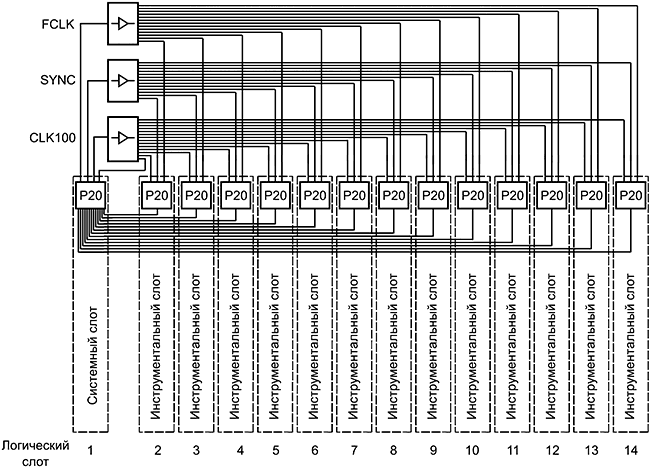

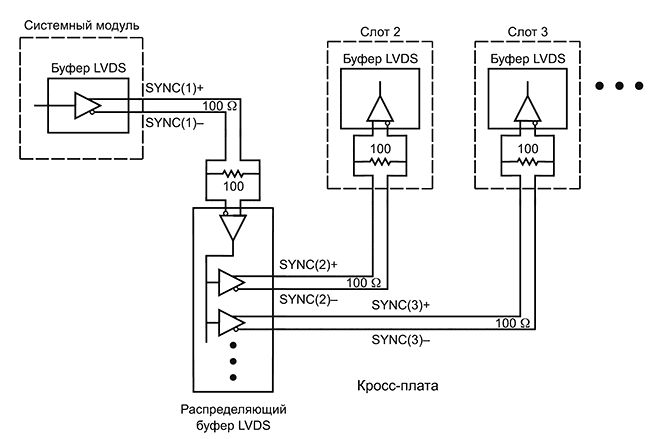

Другое существенное отличие AXIe состоит в реализации интерфейса синхронизации. Интерфейс синхронизации реализован путем радиальной трассировки дифференциальных пар сигналов тактовой частоты (CLK100), синхронизации (SYNC), запуска (STRIG) и тактовой частоты для интерфейсов PCIe (FCLK) между системным слотом и остальными слотами. Интерфейс синхронизации задействует освободившиеся контакты соединителя зоны 2, которые в АТСА использованы для канала обновления, частот синхронизации и каналов fabric слотов 15 и 16. Радиальная трассировка предполагает связь посредством сигнальных линий одного центрального устройства с группой устройств. При этом каждое устройство использует индивидуальную линию для связи с центральным устройством (системным модулем). Топология интерфейса синхронизации показана на рисунке 5.

|

Рисунок 5 - Интерфейс синхронизации AXIe

Радиальные линии CLK100 кросс-платы распространяют по дифференциальным парам тактовую частоту 100 МГц от системного слота к слотам инструментов. Радиальные линии SYNC передают дифференциальный триггерный сигнал от системного слота к слотам инструмента. Для распределения CLK100 и SYNC от системного слота по каждому направлению использован активный буфер, к входу которого подключается индивидуальная сигнальная пара. Радиальные линии STRIG представляют собой двунаправленные дифференциальные пары между системным модулем и слотами инструментальных модулей. Для каждого слота применена индивидуальная дифференциальная пара. Сигналы STRIG не буферизируются и терминируются на системном модуле.

Кросс-платы AXIe обеспечивают распространение опорной тактовой частоты 100 МГц для интерфейсов PCIe по дифференциальным парам сигнала FCLK от системного слота ко всем остальным слотам. Топология сигнала FCLK подразумевает наличие на кросс-плате активного буфера, индивидуально для каждого слота.

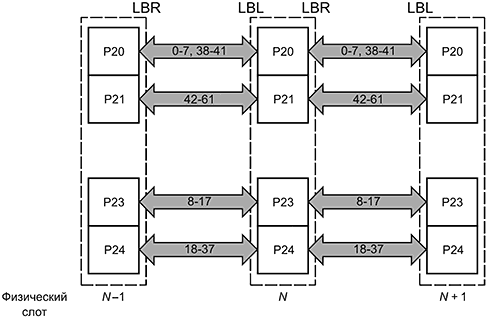

Локальная шина AXIe представляет собой короткие дифференциальные сигнальные пары, соединяющие соседние слоты AXIe, за исключением системного слота. Локальная шина содержит 18 обязательных дифференциальных пар в каждом сегменте "слот-слот". Кросс-платы могут опционально реализовывать расширение локальной шины не более 42 или 62 пар.

Архитектура AXIe не ограничивается только нуждами контрольно-измерительного оборудования общего назначения. Последующие дополнительные стандарты AXIe (AXIe-3.1, AXIe-3.2 и т.д.) будут добавлять дополнительные функции и конфигурации соединителя (или соединителей), расположенных в зоне 3 кросс-платы.

В связи с тем что в AXIe не предусмотрены функции резервирования, как в ATCA, каналы base и fabric концентратора 2 (логический слот 2 в ATCA) не использованы в AXIe. Системы AXIe не поддерживают наличие системного концентратора в логическом слоте 2. В настоящем стандарте логический слот 2 определен как обычный инструментальный слот.

Согласно архитектуре AXIe в устройствах и системах должен быть применен расширенный набор записей электронного ключа для обеспечения совместного использования определенных в AXIe топологий и ресурсов кросс-платы. Кроме того, необходимо, чтобы каждое шасси содержало собственный интеллектуальный менеджер шасси.

Настоящий стандарт содержит требования к ЭМС для модулей и системных компонентов, которые должны предотвращать влияние электромагнитных помех от компонентов внутри шасси AXIe на точность измерений.

Требования соответствия

Все изделия AXIe, включая кросс-платы, шасси и модули, должны удовлетворять требованиям настоящего стандарта. Они также могут удовлетворять требованиям AXIe-2 к ПО. Некоторые изделия AXIe могут дополнительно удовлетворять требованиям будущих расширений стандарта AXIe, таких как AXIe-3.1, который устанавливает дополнительные требования к кросс-плате AXIe изделий, ориентированных на приложения автоматизированного тестирования интегральных микросхем.

Правила использования торговой марки и логотипа AXIe приведены в приложении А.

1 Область применения

Настоящий стандарт предназначен для решения следующих задач:

- обеспечения возможности гибкой конфигурации КИА для получения наилучшей производительности при эксплуатации;

- снижения стоимости разработки и внедрения КИА;

- снижения габаритных размеров контрольно-измерительных комплексов;

- повышения производительности модульных систем путем организации высокоскоростных потоков данных и тестовых сигналов;

- облегчения модификации КИА путем замены или дополнения модифицированных инструментальных модулей при сохранении неизменной структуры всей системы КИА;

- обеспечения возможности разработки систем с применением высокоскоростных интерфейсов Ethernet и PCIe.

1.1 Термины, определения и сокращения

Терминология AXIe большей частью построена на языке, знакомом производителям, системным интеграторам и конечным пользователям индустрии КИА. В некоторых случаях она отличается от унаследованной терминологии из сферы телекоммуникации, используемой в ATCA. Термины, использованные в настоящем стандарте, можно разделить на две группы:

- специфические термины AXIe. Вновь введенные термины, применимые только к оборудованию и системам AXIe;

- термины, заимствованные из ATCA в том же значении, но с учетом особенностей архитектуры AXIe.

Отдельно выделена группа терминов, которые используются в ATCA, но в настоящем стандарте они не приведены и имеют синонимы из группы специфических терминов AXIe. Разработчики должны это учитывать, т.к. при разработке оборудования AXIe им придется пользоваться [1].

Специфические термины AXIe

В настоящем стандарте применены следующие термины с соответствующими определениями:

1.1.1 шасси (chassis): Основной инфраструктурный компонент AXIe, в котором размещаются модули AXIe.

Примечание - Типичное шасси AXIe содержит кросс-плату, носитель модулей, источник(и) питания, блок вентиляции, менеджер шасси и корпус из листового металла. Шасси может содержать элементы для монтажа в стойку, а также встроенный системный модуль.

1.1.2 интегрированное шасси (integrated chassis): Шасси AXIe, которое имеет встроенный системный модуль вместо стандартного системного слота AXIe.

1.1.3 модуль (module): Набор из печатных плат с фронтальной панелью и экранирующими панелями, который вставляется в слот AXIe.

Примечание - Является эквивалентом фронтальной платы (front board) ATCA.

1.1.4 системный модуль (system module): Модуль AXIe, который содержит коммутаторы LAN (LAN switches), коммутаторы PCIe, ресурсы синхронизации системы и триггерных сигналов и/или другие централизованные ресурсы.

Примечание - Системный модуль устанавливается в системный слот шасси. Системный модуль AXIe является эквивалентом платы концентратора (hub board) ATCA.

1.1.5 встроенный системный модуль (embedded system module): Интегрированный в шасси узел, выполняющий функции системного модуля.

1.1.6 системный слот (system slot): Слот AXIe, который поддерживает системный модуль.

Примечание - В AXIe это логический слот 1 (logical slot 1), который является эквивалентом слота концентратора (hub slot) ATCA.

1.1.7 инструментальный модуль (instrument module): Любой модуль AXIe, который не является системным модулем.

1.1.8 инструментальный слот (instrument slot): Слот AXIe, который поддерживает установку только инструментального модуля.

Примечание - B AXIe это логические слоты 2-14.

1.1.9 интерфейс синхронизации AXIe (AXIe timing interface): Набор радиальных сигнальных пар, которые передают синхронизирующие сигналы AXIe между системным слотом и инструментальными слотами.

Примечание - Синхронизирующими являются сигналы CLK100, SYNC, STRIG и FCLK.

1.1.10 шина триггеров AXIe (AXIe trigger bus): Набор из 12 сигнальных пар MLVDS, TRIG(0:11), которые проходят через все слоты кросс-платы AXIe.

1.1.11 локальная шина AXIe (AXIe local bus): Набор из 18, 42 или 62 сигнальных пар, которые соединяют соседние слоты шасси.

1.1.12 CLK100: Набор из сигнальных пар LVDS, которые исходят от системного модуля, буферизуются на кросс-плате AXIe и радиально соединяются со всеми инструментальными модулями.

Примечание - По этим парам транслируется тактовая частота 100 МГц.

1.1.13 SYNC: Набор триггерных/синхронизирующих сигнальных пар LVDS, которые исходят от системного модуля, буферизуются на кросс-плате AXIe и радиально соединяются со всеми инструментальными модулями.

1.1.14 STRIG (star trigger): Набор двунаправленных сигнальных пар LVDS, которые напрямую соединяют системный слот со всеми инструментальными по радиальной топологии.

1.1.15 FCLK (fabric clock): Набор сигнальных пар HCSL, которые исходят от системного модуля, буферизуются на кросс-плате AXIe и радиально соединяются со всеми инструментальными модулями.

Примечание - По этим парам транслируется сигнал опорной тактовой частоты 100 МГц для всех PCIe портов на инструментальных каналах, подключенных к системному слоту.

Термины АТСА, использованные в настоящем стандарте

Ниже приведены термины АТСА, которые использованы в настоящем стандарте применительно к архитектуре AXIe в том же значении, что и для архитектуры АТСА, но с учетом особенности архитектуры первой:

1.1.16 направляющие А1, А2: Центрирующие/направляющие штифты на кросс-плате (А1) и модуле RTM (А2) (только в АТСА), исполняющие также функцию механического ключа, предотвращающего сочленение несовместимых плат.

1.1.17 кросс-плата (backplane): Печатная плата, содержащая соединители зоны 1 и 2, с которыми сочленяются модули при установке в шасси.

Примечание - Плата обеспечивает распределение линий питания, высокоскоростных сигнальных пар и вспомогательных управляющих сигналов между слотами шасси.

1.1.18 основной канал (base channel): Физическое соединение основного интерфейса, состоящее из четырех дифференциальных пар в соединителях J23/P23 и J24/P24 зоны 2.

Примечание - Каналы пронумерованы от 1 до 14. Каждый базовый канал является соединением "точка-точка" между системным слотом (логическим слотом 1) и инструментальными слотами (логические слоты 2-14) шасси.

1.1.19 основной интерфейс (base interface): Интерфейс зоны 2, который используется для обеспечения соединений по протоколам 10/100/1000Base-T Ethernet между системным модулем и инструментальными модулями шасси.

Примечание - Физически основной интерфейс реализуется посредством основного канала на кросс-плате.

1.1.20 нижняя сторона (bottom): Применительно к модулям AXIe и АТСА обозначает сторону платы модуля, которая находится внизу при вертикальной установке в шасси.

1.1.21 канал (channel): Группа дифференциальных пар, которые физически трассируются совместно на кросс-плате и логически объединяются в соединительную магистраль между двумя слотами (или модулями).

Примечание - Основной канал состоит из четырех дифференциальных пар (см. 1.1.18); инструментальный канал - из восьми дифференциальных пар (см. 1.1.27).

1.1.22 сторона 1 печатной платы (component side 1): Применительно к платам AXIe и АТСА обозначает сторону печатной платы модуля, на которую устанавливаются все высокие компоненты.

Примечание - Идентично термину "правая сторона" (см. 1.1.55).

1.1.23 сторона 2 печатной платы (component side 2): Применительно к платам AXIe и АТСА обозначает сторону печатной платы модуля, которая обычно зарезервирована для трассировки печатных проводников через сквозные отверстия, но на которой также могут располагаться низкие компоненты.

Примечание - Идентично термину "левая сторона" (см. 1.1.42).

1.1.24 выделенный контроллер управления шасси (dedicated shelf management controller): Контроллер IPM, расположенный внутри шасси, в месте, отличном от местоположения зарезервированного для размещения контроллера управления шасси.

Примечание - Использование подобного контроллера может быть вызвано аппаратными соображениями (например, проектировщик шасси предполагает включить в менеджер шасси возможность установки адреса шасси) или топологией шины IPMB (IPMB трассируется по топологии звезды).

1.1.25 топология двойной звезды (dual star topology): Топология соединения, в которой два ресурса коммутатора обеспечивают избыточность соединения со всеми конечными точками в сети.

Примечание - Пара плат концентраторов обеспечивает избыточные соединения между узлами.

1.1.26 электронный ключ (electronic keying, сокр. E-Keying): Протокол, используемый для определения совместимости параметров основного и инструментального интерфейсов, а также остальных ресурсов модулей AXIe и АТСА с возможностями шасси, в которые установлены эти модули.

Примечание - Обозначает процесс предоставления необходимых ресурсов для инструментальных модулей на основе анализа информации, хранящейся в FRU модулей и кросс-платы.

1.1.27 инструментальный канал (fabric channel): Физическое соединение инструментального интерфейса, которое может содержать до восьми дифференциальных пар сигналов.

Примечание - Каждый инструментальный слот кросс-платы AXIe поддерживает один инструментальный канал. Системный слот связан через отдельный инструментальный канал с каждым инструментальным слотом шасси. При этом каждый инструментальный канал является соединением "точка-точка". Инструментальные каналы пронумерованы от 1 до 13. Инструментальный канал логически разбивается на четыре порта и может быть однопортовым (содержит две дифференциальные пары), двухпортовым (четыре дифференциальные пары) или полным (восемь дифференциальных пар).

1.1.28 инструментальный интерфейс (fabric interface): Интерфейс зоны 2, который обеспечивает информационный обмен системного модуля/слота с каждым (из 13 возможных) инструментальным модулем/слотом посредством инструментального канала.

Примечание - Кросс-платы AXIe поддерживают для инструментального интерфейса только топологию одиночной звезды. Единственным протоколом обмена по инструментальному интерфейсу для модулей AXIe (в отличие от модулей АТСА) согласно настоящему стандарту может быть только PCIe.

1.1.29 лицевая панель (face plate): Передняя панель модуля, перпендикулярная печатной плате, которая служит для установки соединителей, индикаторов, элементов управления и мезонинов, а также становится преградой для воздушного потока, циркулирующего внутри шасси, и улучшает ЭМС модулей.

1.1.30 блок вентиляторов (fan tray): Конструктивный элемент шасси, содержащий набор вентиляторов, для обеспечения принудительного охлаждения модулей внутри шасси.

1.1.31 устройства FRU (field replaceable unit): Любая часть системы, которая может быть извлечена и заменена пользователем самостоятельно.

Примечание - Не все устройства FRU позволяют их извлекать во время работы системы. Как правило, FRU может не иметь встроенного контроллера IPM и, следовательно, напрямую не контролироваться через инфраструктуру IPMI. Базовые данные инвентаризации таких FRU могут храниться в промежуточном контроллере в другом месте шасси. Примерами такого типа FRU являются части корпуса носителя модулей, узел распределения питания, простые мезонины. FRU, включающие в себя контроллер IPM, - это интеллектуальные FRU, примерами которых служат системные и инструментальные модули, а также блоки вентиляторов, источники питания и платы сигнализации.

1.1.32 данные FRU (field replaceable unit information): Данные, которые описывают и характеризуют параметры FRU, хранящиеся в энергонезависимой памяти FRU.

Примечание - Формат хранения данных описан в документе IPMI Platform Management.

1.1.33 глобальный уникальный идентификатор; GUID: Уникальный идентификатор длиной 128 бит.

Примечание - Идентификаторы GUID в оборудовании АТСА и AXIe создаются и обрабатываются в соответствии со спецификацией IPMI v1.5.

1.1.34 ручка, расположенная на лицевой панели модуля (face plate handle): Ручка, используемая в качестве механического рычага для вставки модуля в шасси и его извлечения из шасси.

1.1.35 защелка (handle switch): Защелка, встроенная в ручку на лицевой панели модуля и используемая для фиксации модуля в шасси.

1.1.36 аппаратный адрес (hardware address): Адрес, назначенный с использованием аппаратных сигналов, поступающих от шасси к модулю.

Примечание - Термин "аппаратный адрес" используется вместо термина "географический адрес", т.к. последний подразумевает связь между набором чисел и набором мест в пределах шасси, которые соответствуют всем шасси системы.

1.1.37 контроллер интеллектуального управления платформой (IPM controller или IPMC): Интеллектуальный узел любого интеллектуального устройства FRU, который реализует интерфейс IPMB-0, производит обработку и маршрутизацию сообщений, содержит информацию о встроенных датчиках и FRU.

Примечание - Контроллер реализует другие необходимые для работы интеллектуального устройства FRU функции. Кроме того, он может содержать интерфейсы к полезной нагрузке конечного устройства и быть связанным с основным интерфейсом устройства.

1.1.38 шина интеллектуального управления платформой; IPMB: Шина низкого уровня для управления оборудованием.

1.1.39 интерфейс интеллектуального управления платформой; IPMI: Механизм для управления, ведения мониторинга и протоколирования параметров работы компонентов компьютерной системы.

1.1.40 улавливающие гнезда К1, К2: Улавливающие гнезда на плате модуля, использующиеся для центрирования/направления модуля при его сочленении с кросс-платой и модулем RTM.

1.1.41 ЛВС; LAN: Локальная вычислительная сеть (например, Ethernet).

1.1.42 левая сторона (left): Применительно к модулям AXIe и АТСА указывает сторону платы, которая будет находиться слева, если смотреть на шасси с вертикальным расположением модулей со стороны лицевых панелей, или спереди.

1.1.43 линия (link): Один или несколько портов, объединенные общим протоколом обмена.

Примечание - Линии представляют собой группы портов, которые активируются и блокируются при помощи протокола электронного ключа.

1.1.44 логическая земля (logic ground): Общая электрическая цепь на кросс-плате и модулях, служащая путем для протекания возвратных токов и задающая опорный уровень для логических сигналов, передающихся между платами.

1.1.45 логический слот (logical slot): Слот в пределах шасси, определяемый аппаратным адресом в зоне 1.

Примечание - Каждый слот имеет уникальный номер от 1 до 14. Логические номера слотов используются для распределения каналов между слотами. Согласно [1] устанавливается прямая связь между номерами каналов и номерами логических слотов. Например, канал 1 (основной или инструментальный) каждого слота устанавливает прямое соединение с логическим слотом 1, который в AXIe всегда зарезервирован под системный модуль.

1.1.46 LVDS: Электрический интерфейс передачи сигналов между двумя узлами по дифференциальной паре.

1.1.47 MLVDS: Расширение стандарта LVDS для передачи сигналов по дифференциальным парам между несколькими узлами (более двух).

1.1.48 полезная нагрузка (payload): Основная функция, которую обеспечивает FRU.

Примечание - Включает в себя аппаратные средства FRU, за исключением того, что связано с управлением. Также может включать в себя прошивку, операционную систему и прикладное ПО, работающее на аппаратном уровне полезной нагрузки.

1.1.49 интерфейсная нагрузка (payload interface): Локальный интерфейс в пределах FRU между полезной нагрузкой и контроллером интеллектуального управления платформой.

1.1.50 физический адрес (physical address): Адрес, определяющий физическое местоположение FRU.

Примечание - Состоит из полей "тип места" и "номер места".

1.1.51 номер физического слота (physical slot number): Определяет физическое расположение слота в пределах шасси.

Примечание - Номера физических слотов начинаются с цифры 1, обозначая самый левый (или самый нижний) физический слот и последовательно увеличивая вправо (или вверх для горизонтально ориентированных слотов). Номер физического слота не обязательно совпадает с его логическим номером. Таблица адресов в записях шасси FRU служит для сопоставления между физическим и логическим номерами каждого слота шасси. Физический номер слота указывают в поле "номер места" в записях таблицы.

1.1.52 управление платформой (platform management): Управление ресурсами и функциями устройств FRU в системе шасси.

1.1.53 порт (port): Минимальное число дифференциальных пар кросс-платы, которые могут быть задействованы при помощи технологии электронного ключа для передачи сигналов и данных.

Примечание - Для основного интерфейса порт состоит из четырех дифференциальных пар. Для инструментального интерфейса один порт содержит две дифференциальные пары.

1.1.54 модуль RTM (rear board or rear transition module, RTM): Модуль трассировки выводов зоны 3 инструментальных модулей на заднюю стенку шасси или модуль тыльного ввода/вывода.

1.1.55 правая сторона (right): Применительно к модулям AXIe и АТСА указывает сторону платы, которая будет находиться справа, если смотреть на шасси с вертикальным расположением модулей со стороны лицевых панелей, или спереди.

1.1.56 информация шасси FRU (shelf FRU information): Таблица записей данных, хранящаяся в шасси FRU и содержащая минимально необходимую информацию по мощности питания шасси, возможностям охлаждения и поддерживаемым кросс-платой соединениям.

1.1.57 менеджер шасси (shelf manager): Узел, ответственный за управление питанием, охлаждением и соединениями (при помощи процедур электронного ключа) в шасси.

Примечание - Менеджер шасси также маршрутизирует сообщения между интерфейсом системного администратора и IPMB-0, предоставляет интерфейсы для системных репозиториев и отвечает на сообщения о событиях. Менеджер шасси может быть частично или полностью реализован на оборудовании контроллера управления шасси ShMC и/или диспетчера системы.

1.1.58

IP-адрес менеджера шасси (shelf manager IP address): IP-адрес версии 4, уникальный для каждого шасси системы, которое поддерживает управление через Ethernet.

Примечание - В любой момент времени этот IP-адрес может быть связан только с одним МАС-адресом.

1.1.59 контроллер управления шасси; ShMC: Контроллер интеллектуального управления платформой IPMC, одновременно реализующий функции менеджера шасси.

1.1.60 диспетчер системы (system manager): Функциональная надстройка над менеджером шасси, которая управляет всей системой в целом независимо от конкретной реализации.

Примечание - Диспетчер системы может быть частично или полностью реализован как на оборудовании контроллера управления шасси, так и в виде отдельного узла.

1.1.61 слот (slot): Месторасположение каждого модуля в шасси.

1.1.62 топология звезда (star): Топология кросс-платы, имеющая один системный слот, соединенный со всеми инструментальными слотами шасси.

1.1.63 носитель модулей (subrack): Механическая несущая конструкция для модулей AXIe и АТСА.

Примечание - Включает в себя обязательные элементы: направляющие для установки модулей и устройств FRU, защиту от электростатических разрядов, направляющие штифты, монтажные крепления для лицевых панелей модулей, электромагнитные экраны и крепления под кросс-плату. Носитель модулей является сборочной единицей шасси.

1.1.64 верхняя сторона (top): Применительно к модулям AXIe и АТСА обозначает сторону платы, которая находится вверху при вертикальной установке модуля в шасси.

1.1.65 зона 1 (zone 1): Часть линейного пространства вдоль высоты слотов АТСА и AXIe, выделенных под питание, управление и другие вспомогательные функции.

1.1.66 соединитель зоны 1 (zone 1 connector): Соединитель J10 на кросс-плате и Р10 на модуле.

1.1.67 зона 2 (zone 2): Часть линейного пространства вдоль высоты слотов АТСА и AXIe, выделенных под интерфейсы передачи данных и синхросигналов.

1.1.68 соединитель зоны 2 (zone 2 connector): Соединители Р20-Р24 на кросс-плате и соединители J20-J24 на модуле.

1.1.69 зона 3 (zone 3): Часть линейного пространства вдоль высоты слотов АТСА и AXIe, выделенных под пользовательские приложения.

1.1.70 соединитель зоны 3 (zone 3 connector): Соединители, определяемые расширяющими стандартами AXIe-3.n.

Термины АТСА, не используемые в AXIe или имеющие другое значение

Часть терминов АТСА не используется при описании систем AXIe, так как в индустрии КИА, где применяются системы AXIe, эти термины могут иметь другое, отличное по смыслу значение. К этим терминам относятся:

1.1.71 фронтальная плата (front board): Эквивалент модуля AXIe.

1.1.72 каркас (frame): Эквивалент стойки (Rack).

1.1.73 плата концентратора (hub board): Эквивалент системного модуля AXIe.

1.1.74 слот концентратора (hub slot): Эквивалент системного слота AXIe.

1.1.75 узловая плата (node board): Эквивалент инструментального модуля AXIe.

1.1.76 узловой слот (node slot): Эквивалент инструментального слота AXIe.

1.1.77 полка (shelf): Эквивалент шасси AXIe.

Сокращения

1.1.78 advanced telecommunications computing architecture; АТСА: Усовершенствованная архитектура для телекоммуникационных вычислений - стандарт на модульные телекоммуникационные системы, разработанный группой PICMG.

1.1.79 advancedTCA extensions for instrumentation and test; AXIe: Расширение АТСА для приложений КИА.

1.1.80 intelligent platform management; IPM: Интеллектуальное управление платформой - процесс, при котором управление ресурсами системы и ее отдельных частей (FRU) производится специальным котроллером* по заданному алгоритму.

________________

* Текст документа соответствует оригиналу. - .

1.1.81 local area network; LAN: Локальная вычислительная сеть.

Примечание - В настоящем стандарте относится к вычислительным сетям Ethernet 10/100/1000Base-T.

1.1.82 LAN extensions for instrumentation; LXI: Расширение LAN для приложений КИА.

1.1.83 peripheral component interconnect; PCI: Взаимосвязь периферийных компонентов - шина ввода-вывода для подключения периферийных устройств к материнской плате компьютера.

1.1.84 PCI express; PCIe: Локальная компьютерная шина расширения, предназначенная для подключения периферийных устройств к системной плате персонального компьютера.

Примечание - PCIe реализует программную модель интерфейса PCI и протокол последовательной передачи данных.

1.1.85 PCI extension for instrumentation; PXI: Расширение PCIe для приложений КИА.

1.1.86 VME (versamodule eurocard) extensions for instrumentation; VXIbus: Расширение шины VME для приложений КИА.

1.1.87 контрольно-измерительная аппаратура; КИА: Совокупность технических средств измерений (измерительных приборов, датчиков и др.) и вспомогательных устройств, предназначенных для контроля и измерения электрических и физических параметров.

1.1.88 программное обеспечение; ПО: Комплекс программ, обеспечивающих обработку или передачу данных при выполнении измерений, контроле параметров и выполнении функционального тестирования при помощи систем КИА.

1.1.89 электромагнитная совместимость; ЭМС: Способность технических средств одновременно функционировать в реальных условиях эксплуатации с требуемым качеством при воздействии на них непреднамеренных электромагнитных помех и не создавать недопустимых электромагнитных помех другим техническим средствам.

2 Требования к конструкции

Модули и шасси AXIe должны удовлетворять соответствующим требованиям ATCA, предъявляемым к конструкции. Некоторые из них не имеют отношения к AXIe, поэтому не включены в настоящий стандарт. В частности, исключены требования к модулям RTM, соединениям зоны 3 и к допустимому уровню звукового шума.

2.1 Основные требования к конструкции

Изделия AXIe должны удовлетворять всем требованиям, включенным в подраздел 2.1 [1].

Правило 2.1 Продукты AXIe-1 должны удовлетворять требованиям 2.1-2.7 [1].

2.2 Требования к конструкции модулей

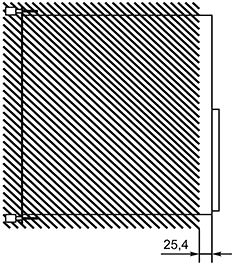

Модули AXIe должны удовлетворять конструктивным требованиям к фронтальным платам ATCA. В связи с тем что системы AXIe-1 не содержат модулей перехода на заднюю стенку (модули тыльного ввода-вывода RTM), модули AXIe-1 не нуждаются в соединителях зоны 3. Однако допускается применение соединений зоны 3 в расширениях AXIe-3.n. Для предотвращения наложений с соединителями зоны 3 и возможных повреждений модулей для модулей AXIe-1 сохранена функция центрирования/управления сочленением с использованием улавливающего отверстия К2. Для модулей AXIe-1 определено значение по умолчанию ключевой позиции в направляющем отверстии К2. Когда расширения AXIe-3.n зоны 3 не используют возможность отверстия K2/A2 центрирования/управления и содержат соединители VHDM со встроенными центрирующими штифтами, для модулей AXIe-1 определена область, показанная на рисунке 2.1, в которой запрещено размещать элементы высотой более 5 мм. Чтобы не допустить наложение с соединителями зоны 3 AXIe-3.n, в модулях AXIe-1 не допускается реализация опционального расширения печатной платы в зоне 3, приведенного на рисунке 1.7 [1].

Правило 2.2 Модули AXIe-1 должны удовлетворять требованиям 2.8, 2.10-2.75, 2.80-2.105 и 2.133 [1] при условии соблюдения дополнительных ограничений, приведенных в настоящем стандарте.

Правило 2.3 На печатной плате AXIe-1 модуля не допускается использовать опциональное расширение области платы в районе зоны 3, определенное в 2.9 [1].

Разрешение 2.1 При необходимости в печатной плате AXIe-1 модуля может быть обеспечена возможность использования опционального расширения области платы в районе лицевой панели, определенного в 2.9 [1].

Правило 2.4 В модулях AXIe-1 не должно быть никаких компонентов высотой более 5 мм, установленных на компонентной стороне 1 печатной платы в пределах области дополнительного ограничения высоты компонента, показанной на рисунке 2.1.

Замечание 2.1 В каждом соединителе зоны 3 кросс-платы AXIe-3.1 имеется встроенный установочный штифт. Этот штифт входит в корпус модуля AXIe-1. Правило 2.4 обеспечивает зазор для данного установочного штифта.

Замечание 2.2 От модулей AXIe-1 не требуется реализация всего функционала "горячей замены" модулей. "Горячая замена" - это возможность сочленения/расчленения модуля с кросс-платой при включенном питании шасси. В частности, не требуются реализация защелок (handle switch), описанных в 2.76 [1], и применение синего светодиода "горячей замены" (Blue Hot-Swap LED).

Разрешение 2.2 Модули AXIe-1 могут полностью обеспечивать возможность поддержания "горячей замены" и реализации защелок в соответствии с 2.76 [1].

|

Примечания

1 Все размеры указаны относительно баз D и F.

2 Все размеры, указанные на этой схеме, являются базовыми и имеют допуски 0,13 DE.

Рисунок 2.1 - Область компонента дополнительных ограничений высоты для модулей AXIe-1

Правило 2.5 Модули AXIe-1, содержащие в себе защелки для полной поддержки возможностей "горячей замены", должны удовлетворять требованиям 2.76-2.79 [1].

Правило 2.6 Модуль AXIe-1, не имеющий защелки, должен обеспечивать возможность виртуального входа для IPM-контроллера модуля и программной имитации защелок (виртуальных защелок) с постоянной передачей состояния, по которому переключатель находится в позиции "закрыто".

2.2.1 Светодиоды и маркировка лицевой панели AXIe

В модулях AXIe-1 могут быть не предусмотрены светодиоды на лицевой панели, кроме светодиода LED 1, определенного в ATCA. Решение о положении и цвете любых светодиодов лицевой панели, кроме обязательного LED 1, принимает разработчик. Из-за плотности разъемов ввода-вывода, необходимых для тестирования и измерений, предполагается, что светодиоды будут располагаться близко к верху или низу лицевой панели модуля.

Разрешение 2.3 Модули AXIe-1 могут удовлетворять требованиям 2.106-2.132 [1].

Правило 2.7 На лицевой панели модуля AXIe-1, реализующего возможность "горячей замены" (сочленение/расчленение модуля с кросс-платой при включенном питании шасси), должен быть синий светодиод (blue led) на лицевой панели, удовлетворяющий требованиям 2.112-2.113 [1].

Правило 2.8 На лицевой панели каждого модуля AXIe-1 должен быть светодиод LED 1, удовлетворяющий требованиям 2.115-2.118 [1].

2.3 Модули тыльного ввода-вывода (RTM)

Архитектурой AXIe-1 не предусмотрено использование модулей тыльного ввода-вывода или подключение других модулей к разъемам зоны 3. Раздел 2.3 [1] не применим к архитектуре AXIe-1.

Правило 2.9 Модули AXIe-1 не должны иметь никаких соединителей в районе зоны 3.

2.4 Соединители кросс-платы

Архитектура AXIe включает в себя соединители зоны 1 и зоны 2 архитектуры АТСА. Некоторые специфические телекоммуникационные сигналы в соединителе зоны 1 не используются в AXIe. Введены сигналы для соединителей зоны 2 AXIe, которые не используются в архитектуре АТСА.

2.4.1 Соединитель зоны 1

В устройствах и системах АХlе-1 использованы цепи питания, сигналы для аппаратного управления и разряды физического адреса слота, предоставляемые соединителем зоны 1. В устройствах и системах АХlе-1 не применяются контакты зоны 1, предназначенные для организации процессов самоконтроля ("metallic test", "ringin generator").

Правило 2.10 Модули и объединительные панели АХlе-1 должны удовлетворять требованиям 2.267-2.274, 2.297 и 2.299 [1].

Замечание 2.3 Системы АХlе-1 не должны реализовывать резервные линии питания или аппаратного управления. Модули и системы АХlе-1 должны реализовывать и подключать ресурсы АТСА, обозначенные суффиксом "_А". Использование ресурсов, обозначенных суффиксом "_В", опционально.

Соединитель зоны 1 определен в приложении В [1] с физическими размерами соединителя фронтальной платы, указанными в таблице В.5. Для лучшей совместимости AXIe необходимо, чтобы контакты соединителя имели жесткие допуски.

Правило (2.0) 2.1 Контакты соединителя зоны 1 фронтальной платы с номинальным диаметром 1,6 мм (соответствует диаметру Е, приведенному в таблице В.5 приложения В [1]) должны иметь диаметр в диапазоне от 1,562 до 1,613 мм.

Правило (2.0) 2.2 Контакты соединителя зоны 1 фронтальной платы с номинальным диаметром 0,76 мм (соответствует диаметру F, приведенному в таблице В.5 приложения В [1]), должны иметь диаметр в диапазоне от 0,749 до 0,775 мм.

2.4.2 Соединитель зоны 2

Системы АХlе-1 используют такие же соединители зоны 2, как и АТСА.

Правило 2.11 Модули и кросс-платы АХlе-1 должны удовлетворять требованиям 2.300-2.302 [1].

2.4.3 Соединитель зоны 3

В системах АХlе-1 не используются ресурсы зоны 3. Однако расширения стандарта AXIe-3.n допускают использование зоны 3 для приложений при необходимости. Размеры соединителей, используемых в зоне 3 на кросс-плате AXIe-3.n, ограничены таким образом, чтобы они не мешали установке в шасси модулей АХlе-1 без соединителей в зоне 3. Также шасси АХlе-1 должны конструктивно допускать установку модулей АТСА и AXIe-3.n, которые имеют соединители зоны 3.

Замечание 2.4 Последующие стандарты AXIe-3.n, которые будут определять соединения зоны 3, должны удовлетворять требованиям 2.303-2.313 [1].

Замечание 2.5 Для совместимости с модулями АХlе-1 соединители зоны 3 AXIe-3.n кросс-платы должны быть расположены в пределах границ области расположения, определенной на рисунке 2.2. Это относится к соединителям, предназначенным для стыковки с инструментальным модулем, но не к соединителям модулей RTM AXIe-3.n. Область расположения соединителя на модуле RTM определена [1]. АТСА конструктивно не допускает установку модулей АХlе-1 в слоты с установленными модулями RTM, поэтому на расположение соединителей RTM в AXIe-3.n шасси не накладываются ограничения.

2.4.4 Центрирование и управление стыковкой

Системы АХlе-1 должны реализовывать принципы механического управления стыковкой кроссплаты и сочленяемых модулей, используемых в АТСА [1]. Для этого используются штифты на кроссплате А1 и на RTM А2 с определенной формой сечения и уловители с отверстиями на инструментальных модулях К1 и К2. Если форма штифта совпадает с формой отверстия уловителя, то стыковка разрешается, в противном случае - не разрешается.

Правило 2.12 Модули и кросс-платы АХlе-1 должны удовлетворять требованиям 2.314-2.324, 2.328-2.329 и 2.331-2.338 [1].

Модули АХlе-1 не имеют соединителей зоны 3 и должны разрабатываться таким образом, чтобы механически не пересекаться с соединителями зоны 3 кросс-платы AXIe-3.n. Модуль должен быть снабжен выравнивающими уловителями (alignment receptacle) такой формы, чтобы предотвратить возможность их установки в шасси АТСА с несовместимым модулем RTM или соединителем зоны 3 на кросс-плате. Значение ключевой позиции в отверстии уловителя К2 по умолчанию для модулей АХlе-1 равно "5х", где "х" представляет собой круглое отверстие в уловителе, которое будет вмещать одно из положений ключа (1-8) (см. таблицу 2.14 [1] для определения положения ключевых позиций). В зоне 3 кросс-платы АХlе-3.1 использованы соединители со встроенными выравнивающими штифтами (alignment posts). Для таких кросс-плат может потребоваться удаление выравнивающего уловителя К2 на модулях АХlе-1, в противном случае он будет пересекаться с корпусом соединителя, мешая сочленению.

|

Рисунок 2.2 - Расположение соединителя зоны 3 кросс-платы AXle-3.n

Последующие стандарты AXIe-3.n (где n>1), устанавливающие зону 3 кросс-платы, должны определять использование выравнивающих штифтов А2 со значением "5n".

Правило 2.13 Модули АХlе-1 должны иметь установленные производителем выравнивающие уловители К2 со значением ключевой позиции, равным значению по умолчанию "5х".

Замечание 2.6 Требование 2.338 [1] обязывает обеспечить легкую замену А2 и К2 элементов без специальных приспособлений.

2.5 Кросс-платы

Кросс-платы АХlе-1 могут обеспечивать возможность установки системного модуля в стандартный слот AXIe или иметь системные ресурсы, встроенные в саму кросс-плату. Позиции слотов AXIe должны удовлетворять конструктивным требованиям [1]. Архитектура AXIe оптимизирована для носителей модулей, которые могут быть установлены в стандартные стойки серии 482,6 мм. Это ограничивает максимальное число поддерживаемых архитектурой АХlе-1 вертикальных слотов до 14.

Правило 2.14 Позиции слотов открытой системы кросс-платы АХlе-1 должны удовлетворять требованиям 2.339 и 2.241-2.346 [1].

Правило 2.15 Кросс-платы АХlе-1 должны предоставлять не более 14 слотов AXIe.

Использование только 14 слотов освобождает ресурсы инструментального интерфейса, которые в АТСА использованы для связи со слотами 15-16. AXIe использует эти контакты на слоте системного модуля для трассировки сигналов STRIG. На остальных слотах эти контакты использованы для локальной шины AXIe.

Замечание 2.7 Нумерация другого слота или другой специфической позиции выходит за рамки настоящего стандарта.

2.6 Носители модулей

Носители модулей АХlе-1 должны поддерживать модули AXIe в соответствии с требованиями [1] к несущим конструкциям для фронтальных плат. Однако системы АХlе-1 не подразумевают использования модулей RTM. Как и для кросс-плат, в носителях модулей допускается совмещать специфические пользовательские и стандартные слоты.

Носители модулей АТСА используются в относительно статичных условиях окружающей среды. Системы AXIe предполагается применять в гораздо более широких диапазонах варьирования условий окружающей среды. Несмотря на то что проектирование носителей в соответствии с тестами целостности АТСА является разумным подходом, реальные условия среды для систем AXIe определяет системный интегратор. Следовательно, от носителей модулей AXIe не требуется соответствие тестам целостности АТСА.

Правило 2.16 Позиции слотов носителя модуля АХlе-1 должны удовлетворять требованиям 2.347, 2.349-2.351, 2.353-2.354, 2.357-2.364, 2.367, 2.369-2.386, 2.388, 2.390-2.397, 2.404-2.406 и 2.408 [1].

2.7 Шасси

Кроме требований к носителю модулей и кросс-плате, которые обеспечивают совместимость с модулями AXIe, не существует других конструктивных ограничений на шасси AXIe. Функциональность шасси определяется производителем. К шасси AXIe не применяется ни одно из требований подраздела 2.7 [1].

Замечание 2.8 В шасси AXIe допускается реализация поддержки АТСА модулей RTM.

3 Управление аппаратной платформой

Архитектура AXIe включает в себя функции управления аппаратной платформой АТСА. Системы AXIe не требуют полной поддержки возможностей "горячей замены" АТСА. Однако модуль FRU должен обеспечивать поддержку всех рабочих состояний, требуемых для фронтальных плат АТСА. Единственным аппаратным отличием является отсутствие требований к наличию сенсоров, определяющих моменты установки или необходимость удаления модуля из шасси, и голубого светодиода "горячей замены". Для простых модулей с малым потреблением не требуется поддержка функций управления аппаратной платформой.

Архитектура AXIe подразумевает использование протокола PCIe на инструментальном интерфейсе. На модули AXIe, содержащие инструментальный интерфейс PCIe, налагаются дополнительные технические требования [2]. В архитектуре AXIe введены расширения в систему команд управления платформой, необходимые для правильного конфигурирования каналов PCIe, синхронизирующих и триггерных линий AXIe и локальной шины AXIe.

Конфигурация интерфейса триггерных сигналов AXIe не управляется процессом электронного ключа. Управление использованием шиной триггеров и проверка того, что в данный момент времени шиной управляет только одно устройство, выполняются прикладным ПО хост-компьютера.

Примечание - Интерфейс триггерных сигналов содержит шину Trigger Bus - 12 параллельных пар MLVDS сигналов, проходящих через все модули (т.е. источником сигнала может стать любой модуль без вмешательства системного модуля).

Модули и шасси AXIe не используют metallic test bus, ringing bus и частоты синхронизации, входящие в состав timing interface АТСА. Поэтому не требуется реализация поддержки команд и записей, связанных с этими ресурсами в процессах электронного ключа.

Шасси АХlе-1 должны содержать выделенный менеджер шасси с интерфейсом 10/100/1000Base-T LAN. Этот интерфейс может быть подключен к порту ShMC системного слота либо выведен на внешний соединитель. Допустимо наличие дополнительного менеджера шасси. Также менеджер(ы) шасси может (могут) иметь дополнительные интерфейсы LAN.

Правило 3.1 Модули и шасси АХlе-1 должны удовлетворять требованиям 3.1-3.509 и 3.543-3.777 [1] при условии соблюдения дополнительных ограничений настоящего стандарта.

Правило 3.2 Модули АХlе-1, содержащие инструментальный интерфейс PCIe, должны удовлетворять требованиям раздела 4 [2] при условии соблюдения дополнительных ограничений настоящего стандарта.

Правило 3.3 Каждое шасси АХlе-1 должно содержать как минимум один выделенный менеджер шасси.

Правило 3.4 Менеджер шасси АХlе-1 должен обеспечивать по меньшей мере один доступный извне IEEE 802.3 интерфейс менеджера системы, подключенный или к порту ShMC системного слота, или к внешнему соединителю.

Разрешение 3.1 Шасси АХlе-1 может содержать дополнительный менеджер шасси, подключенный или к порту системного слота ShMC, или к внешним LAN-соединителям, или к обоим.

3.1 Процесс электронного ключа

В системах АХlе иначе, чем в системах АТСА, использованы некоторые ресурсы зоны 2, причем их применение накладывает дополнительные требования на процесс электронного ключа.

3.1.1 Процесс электронного ключа

Процесс электронного ключа AXIe является расширением процесса электронного ключа АТСА. Ввиду наличия дополнительных интерфейсов AXIe, менеджер шасси содержит дополнительные команды IPMI для подключения/отключения интерфейсных портов кросс-платы AXIe. Также существует несколько определенных в AXIe записей, добавленных в информацию для шасси и модуля FRU. Эти записи описывают подключение "точка-точка" для интерфейсов AXIe синхронизации и локальной шины, а также содержат дополнительную информацию о каналах PCIe. В менеджере шасси AXIe использованы команды AXIe Set Port State и AXIe Get Port State в дополнение к командам Set Port State и Get Port State ATCA.

Правило 3.5 Информация FRU шасси AXIe-1 должна содержать записи AXIe Backplane Point-to-Point Connectivity Records, описывающие подключение локальной шины и интерфейса синхросигналов, а также подключение любого инструментального канала, отвечающего требованиям к максимальной скорости передачи 5 Гт/с (гигатранзакций в секунду) или 8 Гт/с линий PCIe. Каждый из этих инструментальных каналов должен иметь только один (1) дескриптор канала AXIe (channel descriptor), основанный на максимальной пропускной способности канала.

Замечание 3.1 Подключение инструментального канала АХlе-1 также описано в обязательных записях АТСА Backplane Point-to-Point Connectivity Record. Каналы, отвечающие требованиям 5 или 8 Гт/с, должны содержать дискрипторы* обоих типов: AXIe и АТСА Backplane Point-to-Point Connectivity Descriptors.

________________

* Текст документа соответствует оригиналу. - .

Правило 3.6 Информация модуля АХlе-1 должна содержать записи AXIe Board Point-to-Point Connectivity Records, которые описывают порты локальной шины модуля, порты интерфейса синхронизации и все реверсивные порты PCIe со скоростями 5 или 8 Гт/с.

Правило 3.7 Информация FRU шасси АХlе-1 должна содержать записи AXIe Board Point-to-Point Connectivity Record, связанные с физическим адресом 10h, которые описывают подключение сигналов FCLK, CLK100 и SYNC к буферам распределения синхросигналов кросс-платы.

Правило 3.8 Контроллеры IPM в модулях АХlе-1, управляющие подключением любого порта интерфейса синхронизации AXIe, локальной шины и реверсивных линий PCIe 5 и 8 Гт/с инструментальных каналов, должны поддерживать процесс электронного ключа, используя команды AXIe Set Port State и AXIe Get Port State.

Правило 3.9 Менеджер шасси/IРМ-контроллеры модулей АХlе-1 должны формировать/отвечать на команду AXIe Set Port State в соответствии с требованиями 3.468-3.473 [1] к формированию/ответу на команду Set Port State.

3.1.2 Соединение "точка-точка"

Архитектура AXIe использует модель подключения каналов АТСА. Она включает основной и инструментальный каналы, определенные в АТСА, а также канал локальной шины. Характеристики каналов и портов приведены в таблице 3.1.

Таблица 3.1 - Свойства каналов AXIe соединения "точка-точка"

Тип канала | Число пар на канал | Число пар на один порт | Максимальное число портов на канал | Число каналов на слот |

Основной | 4 | 4 | 1 | 1-14 |

Инструментальный | 8 | 2 | 4 | 1-13 |

Локальная шина | 18 | 18 | 1 | 0-2 |

42 | 42 | 1 | 0-2 | |

62 | 62 | 1 | 0-2 | |

Синхронизация | 1 | 1 | 1 | 4 |

3.1.3 Запись Backplane Point-to-Point Link Connectivity Record

Для основного и инструментального интерфейсов AXIe процесс электронного ключа использует АТСА Backplane Point-to-Point Connectivity Record. Формат этой записи не определяет дескриптор слота для локальной шины AXIe, а также не содержит средства идентификации инструментальных каналов для второго (5 Гт/с) и третьего (8 Гт/с) поколений PCIe. Для описания соединений локальной шины AXIe и высокопроизводительных инструментальных каналов использована запись AXIe Backplane Point-to-Point Connectivity Record. Информация FRU шасси AXIe содержит обе записи АТСА и AXIe Backplane Point-to-Point Connectivity Record. Запись AXIe Backplane Point-to-Point Connectivity Record, приведенная в таблице 3.2, похожа на запись АТСА Backplane Point-to-Point Connectivity Record и включает множество подобных полей с определениями.

Таблица 3.2 - Запись AXIe Backplane Point-to-Point Connectivity Record

Смещение, байт | Длина, байт | Определение |

0 | 1 | ID типа записи (record type ID) (по [1]) |

1 | 1 | Конец списка/версия (end of list/version) (по [1]) |

2 | 1 | Длина записи (по [1]) |

3 | 1 | Контрольная сумма записи (record checksum) (по [1]) |

4 | 1 | Контрольная сумма заголовка (header checksum) (по [1]) |

5 | 3 | ID производителя (по [1]). Использована AXIe Consortium’s IANA Private Enterprise Number, 35609 (008B19h) |

8 | 1 | AXIe ID записи (AXIe record ID). Использовано значение 00h |

9 | 1 | Версия формата записи (record format version). Использовано значение OOh |

10 | m | AXIe Point-to-Point Slot Descriptor List (формат пo [1]) |

В таблице 3.3 описан формат AXIe Point-to-Point Slot Descriptor.

Таблица 3.3 - AXIe Point-to-Point Slot Descriptor

Смещение, байт | Длина, байт | Определение |

0 | 1 | Тип канала AXIe "точка-точка": 00h: зарезервировано 01h: 5 Гт/с инструментальный однопортовый интерфейс 02h: 5 Гт/с инструментальный двухпортовый интерфейс 03h: 5 Гт/с полный инструментальный интерфейс 04h: зарезервировано 05h: 8 Гт/с однопортовый инструментальный интерфейс 06h: 8 Гт/с двухпортовый инструментальный интерфейс 07h: 8 Гт/с полный инструментальный интерфейс 08h-0Fh: зарезервировано 10h: интерфейс локальной шины AXIe с 18 парами 11h: интерфейс локальной шины AXIe с 42 парами 12h: интерфейс локальной шины AXIe с 62 парами 13h-17h: зарезервировано 18h: интерфейс синхронизации AXIe 19h-FFh: зарезервировано |

1 | 1 | Адрес слота (slot address) (по [1]) |

2 | 1 | Число каналов "точка-точка" (Point-to-Point Channel Count) (по [1]) |

3 | 3·n | Дескрипторы канала "точка-точка" (Point-to-Point Channel Descriptors) (формат по [1]) |

Записи Backplane Point-to-Point Channel Descriptor для инструментальных каналов идентичны записям АТСА Backplane Point-to-Point Channel Descriptors. Записи для интерфейсов AXIe перечислены в таблице 3.4.

Таблица 3.4 - AXIe Point-to-Point Channel Descriptor

Биты | Описание |

23:18 | Зарезервированы. Всегда 0 |

17:13 | Локальный канал Локальная шина AXIe: 1(00001b): левый канал 2(00010b): правый канал |

17:13 | Локальный канал Интерфейс синхронизации AXIe: 1(00001b): FCLK 2(00010b): CLK100 3(00011b): SYNC 4(00100b): STRIG (только для инструментальных слотов) 5(00100b): CLK100_FB (только для системных слотов) 7(00111b)-19(10011b): STRIG(2)-STRIG(14) (только для системных слотов) |

12:8 | Удаленный канал Для FCLK, CLK100 и SYNC номер удаленного канала аналогичен номеру локального канала. Для логического слота 1 (физический адрес 41h) номером удаленного канала является значение данного поля. Иначе номер удаленного канала задается выражением: CR=(SL-40h)·3+С, где CR - номер удаленного канала; SL - номер слота (значение local slot number, смещение 1 в AXIe point-to-point slot descriptor); C - значение удаленного канала, определенное в данном поле |

7:0 | Удаленный слот Всегда равно 10h для FCLK, CLK100 и SYNC. Определяет подключение к буферу кросс-платы вместо удаленного слота |

Правило (2.0) 3.1 Каналы интерфейса синхронизации AXIe - FCLK, CLK100 и SYNC - должны быть описаны в дескрипторе слота AXIe point-to-point slot descriptors для каждого физического AXIe слота.

Замечание (2.0) 3.1 В записи Backplane Point-to-Point Connectivity Record не содержится AXIe point-to-point slot descriptor для буферов FCLK, CLK100 и SYNC кросс-платы (по физическому адресу 10h). Поэтому каналы, подключаемые к буферам, должны быть описаны в каждом дескрипторе AXIe point-to-point slot descriptor слота.

Замечание (2.0) 3.2 Поле удаленного канала недостаточно широко, чтобы вмещать диапазон (0-42) спецификаторов канала сигналов буферов кросс-платы. Поэтому актуальный удаленный канал формируется в соответствии с заданными значениями, определенными в таблице 3.4.

3.1.4 Запись Board Point-to-Point Connectivity Record АТСА

Для основных и возможных инструментальных интерфейсов на однослотовых модулях AXIe для процесса электронного ключа использована запись Board Point-to-Point Connectivity Record, как определено в [1].

3.1.5 Расширенная запись Board Point-to-Point Connectivity Record

Схема электронного ключа АТСА не обеспечивает поддержку фронтальных плат, которые используют соединители зоны 2 в нескольких соседних слотах (многослотовые). Для таких модулей необходимо применять запись Extended АТСА Board Point-to-Point Connectivity Record для интерфейсов, поддерживаемых форматом этой записи. Запись Extended АТСА Board Point-to-Point Connectivity Record, описанная в таблице 3.5, содержит поле, определяющее соответствующую позицию слота в интерфейсе соединителя зоны 2, описываемого записью. Для однослотовых модулей AXIe могут быть использованы как стандартная запись АТСА Board Point-to-Point Connectivity Record, так и Extended АТСА Board Point-to-Point Connectivity Record. В отличие от стандартной АТСА, Extended AdvancedTCA Board Point-to-Point Connectivity Record определена как запись AXIe OEM и содержит ID производителя AXIe (AXIe Manufacturer ID) в заголовке.

Таблица 3.5 - Запись Extended АТСА Board Point-to-Point Connectivity Record

Смещение, байт | Длина, байт | Определение |

0 | 1 | Record type ID (по [1]) |

1 | 1 | End of list/version (пo [1]) |

2 | 1 | Record length (пo [1]) |

3 | 1 | Record checksum (пo [1]) |

4 | 1 | Header checksum (пo [1]) |

5 | 3 | Manufacturer ID (пo [1]). Использована AXIe Consortium’s IANA Private Enterprise Number, 35609 (008B19h) |

8 | 1 | AXIe record ID. Использовано значение 02h |

9 | 1 | Record format version. Использовано значение 00h |

10 | 1 | Номер физического слота (соответствующий номеру физического слота IPMC "n") 00h: физический слот n 01h: физический слот n+1 02h: физический слот n+2 ... 0Eh: физический слот n+14 0Fh: физический слот n+15 10h-EFh: зарезервировано F0h: физический слот n-16 F1h: физический слот n-15 ... FEh: физический слот n-2 FFh: физический слот n-1 |

11 | 1 | OEM GUID Count (по [1]) |

12 | 16*n | OEM GUID List (по [1]) |

12+16*n | т | Link Descriptor List (формат пo [1]) |

Правило (2.0) 3.2 Для многослотовых модулей AXIe необходимо использовать запись Extended АТСА Board Point-to-Point Connectivity Record для своих основного и инструментального интерфейсов.

Разрешение (2.0) 3.1 Для однослотового модуля AXIe можно использовать как стандартную, так и расширенную АТСА Board Point-to-Point Connectivity Record запись для своих основного и инструментального интерфейсов.

3.1.6 Запись AXIe Board Point-to-Point Connectivity Record

Для основного и инструментального интерфейсов в процедуре электронного ключа AXIe должна быть использована запись АТСА Board Point-to-Point Connectivity Record. Но формат этой записи не определяет Link Descriptor для локальной шины AXIe, а также не позволяет различать восходящие и нисходящие порты PCIe или 2,5; 5,0 и 8,0 Гт/с порты PCIe. Для описания портов локальной шины AXIe - FCLK, CLK100, SYNC и STRIG портов, а также портов PCIe использована запись AXIe Board Point-to-Point Connectivity Record. Информация для модулей FRU AXIe содержит обе записи АТСА и AXIe Board Point-to-Point Connectivity Record. Информация шасси FRU AXIe также содержит записи Board Point-to-Point Connectivity Record для его буферов распределения сигналов FCLK, CLK100 и SYNC. AXIe Board Connectivity Record имеет две версии, которые очень похожи на записи АТСА Backplane Connectivity Record и содержат множество подобных определений полей. Версия 00 для однослотовых модулей AXIe описана в таблице 3.6.

Таблица 3.6 - Запись AXIe Board Point-to-Point Connectivity Record (версия 00) для однослотовых подключений

Смещение, байт | Длина, байт | Определение |

0 | 1 | Record type ID (по [1]) |

1 | 1 | End of list/version (пo [1]) |

2 | 1 | Record length (пo [1]) |

3 | 1 | Record checksum (пo [1]) |

4 | 1 | Header checksum (пo [1]) |

5 | 3 | Manufacturer ID (пo [1]). Использована запись AXIe Consortium’s IANA Private Enterprise Number, 35609 (008B19h) |

8 | 1 | AXIe record ID. Использовано значение 01h |

9 | 1 | Record format version. Использовано значение 00h |

10 | 1 | OEM GUID Count (пo [1]) |

11 | 16*n | OEM GUID list (пo [1]) |

11+16*n | т | Link descriptor list (формат пo [1]) |

Модули AXIe могут занимать несколько слотов кросс-платы. Для того чтобы контроллер IPMC многослотового модуля поддерживал процесс электронного ключа для всех плат модуля, для каждого занимаемого слота должны быть соответствующие записи Board Point-to-Point Connectivity Record. Для описания каждого соединения модуля с внешними ресурсами, для всех его портов локальной шины, портов FCLK, CLK100, SYNC и STRIG, а также для инструментальных портов PCIe должна быть использована запись AXIe Board Point-to-Point Connectivity Record версии 01. Информация для FRU многослотового модуля AXIe должна содержать версию 01 записи AXIe Board Point-to-Point Connectivity Record для каждой платы модуля. Версия 01 для однослотовых и многослотовых модулей AXIe описана в таблице 3.7.

Таблица 3.7 - Запись AXIe Board Point-to-Point Connectivity Record (версия 01) для многослотовых соединений

Смещение, байт | Длина, байт | Определение |

0 | 1 | Record type ID (по [1]) |

1 | 1 | End of list/version (пo [1]) |

2 | 1 | Record length (пo [1]) |

3 | 1 | Record checksum (пo [1]) |

4 | 1 | Header checksum (пo [1]) |

5 | 3 | Manufacturer ID (пo [1]). Использована запись AXIe Consortium’s IANA Private Enterprise Number, 35609 (008B19h) |

8 | 1 | AXIe record ID. Использовано значение 01h |

9 | 1 | Record format version. Использовано значение 01h |

10 | 1 | Номер физического слота (соответствует IPMC’s номеру физического слота "n") 00h: физический слот n 01h: физический слот n+1 02h: физический слот n+2 ... 0Eh: физический слот n+14 0Fh: физический слот n+15 10h-EFh: зарезервировано F0h: физический слот n-16 F1h: физический слот ot n-15 ... FEh: физический слот t n-2 FFh: физический слот t n-1 |

11 | 1 | OEM GUID count (по [1]) |

12 | 16*n | OEM GUID list (по [1]) |

12+16*n | m | Link descriptor list (формат пo [1]) |