ГОС Г Р 50833-95

ГОСУДАРСТВЕННЫЙ СТАНДАРТ РОССИЙСКОЙ ФЕДЕРАЦИИ

ИНТЕРФЕЙС МНОГОУРОВНЕВЫЙ СИСТЕМНЫЙ мси СИСТЕМЫ ЭЛЕКТРОННЫХ МОДУЛЕЙ

ОБЩИЕ ТРЕБОВАНИЯ К ЛОГИЧЕСКОЙ ОРГАНИЗАЦИИ

Издание официальное

5

ГОССТАНДАРГ РОССИИ Москва

HMri'SPXU OS

II p e д и с л о в н с

I РАЗРАБОТАН II ВНЕСЕН Техническим комитетом по стандартизации ТК 323 «Авиационная техника»

2 УТВЕРЖДЕН И ВВЕДЕН В ДЕЙСТВИЕ Постановлением I нестандарта Российской Федерации от 31.10.95 № 557

3 ВВЕДЕН ВПЕРВЫЕ

•^ ПИК И идл1сль». ню сганлиртов. I09o

HacTosuuni стандарт нс может ныть пи шостыи иди ■iai-iu,iii<i потиром ihc ich. inpa жироклн и paciipix.-) ранги и качестве iM|»iuiia.ii.iii>io истина щч разрешении lucciaif тарга 1’оссии

II

ГОСТ Р 50833 -95

Содержание

I Область применения и назначение............... I

2 Обозначения и сокращения ................. 2

3 Основные характер wet ики....... 6

4 Структура и состав логических средств............. 6

5 Протокол арбитража на параллельной магистрали . . . . 17

6 Протокол иикла передачи данных на параллельной магистрали . ... 25

7 Протоколы диагностирования и инициализации на параллельной магистрали .......... 44

8 Протокол последовательной магистрали............48

9 Протокол взаимодействия в системах на базе интерфейса МСИ . . . . 56

Приложение А Примеры модулей, магистралей и систем, реализуемых с по-мощью интерфейса МСИ............73

Приложение Б Временные диаграммы функционирования логических средств интерфейса МСИ...............77

III

ГОСТ Р 50833-95

ГОСУДАРСТВЕННЫЙ СТАНДАРТ РОССИЙСКОЙ ФЕДЕРАЦИИ

ИНТЕРФЕЙС МНОГОУРОВНЕВЫЙ СИСТЕМНЫЙ МСИ СИСТЕМЫ ЭЛЕКТРОННЫХ МОДУЛЕЙ

Общие требовании к логической оргаккикии

MSI multilevel system interface irf electronic modules system. Genera) requirements Гог logical organization

Дата введения 1996—07—01

1 ОБЛАСТЬ ПРИМЕНЕНИЯ И НАЗНАЧЕНИЕ

1.1 Настоящий стандарт распространяется на интерфейс МСИ магистрально-модульных одно- и многопроцессорных информационно-измерительных и управляющих систем (далее — интерфейс МСИ).

1.2 Интерфейс МСИ, предназначенный для сопряжения с малой избыточностью составных частей систем (электронных модулей) магистрально-модульных радиоэлектронных средств, представляет собой согласованный иерархический ряд по уровням сложности как логических протоколов, так и вариантов физической реализации.

1.3 Интерфейс МСИ является многофункциональным интерфейсом и используется в качестве:

- внутрисистемного, системного и межсистемного интерфейса;

- периферийного интерфейса устройств ввода-вывода;

- интерфейса программируемых приборов.

1.4 Интерфейс МСИ применим в системах с произвольной совокупностью магистралей и модулей. Он независим от конкретных типов микропроцессоров, архитектуры и структуры устройств, оптимизирован под задачи осуществления коммуникаций. Интерфейс МСИ создает основу для унификации программного обеспечения через унификацию архитектуры модулей, вводя стандартный набор регистров управления-статуса и базовых коммуникационных протоколов

Излаик официальное

ГОСТ Р 50833-95

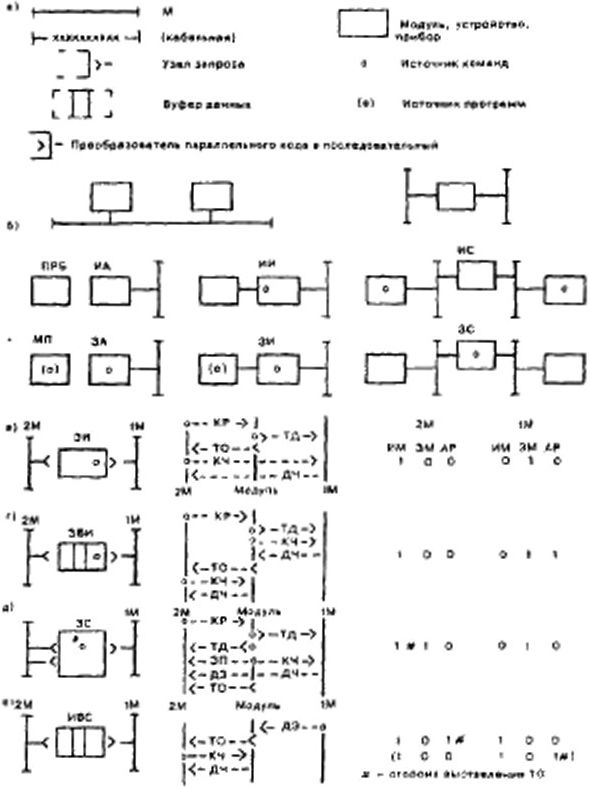

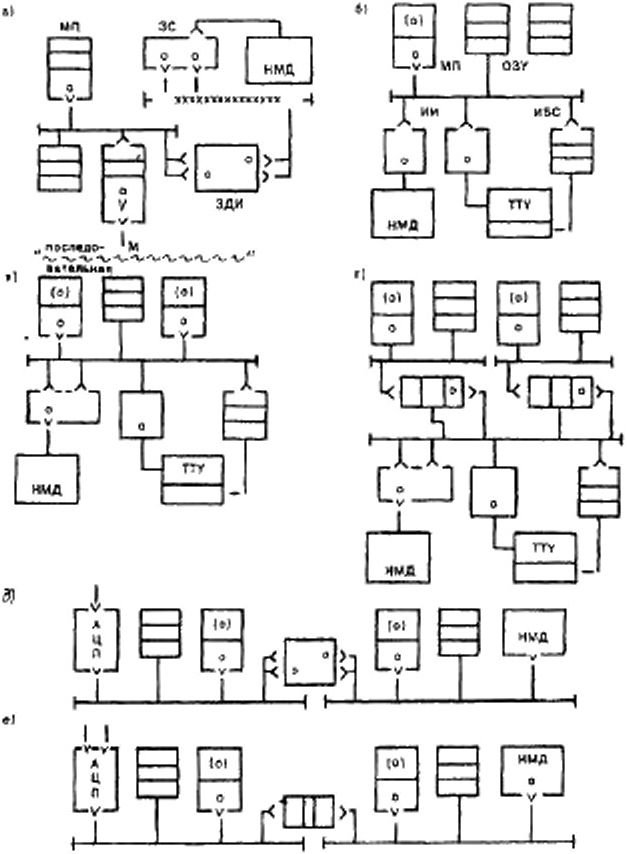

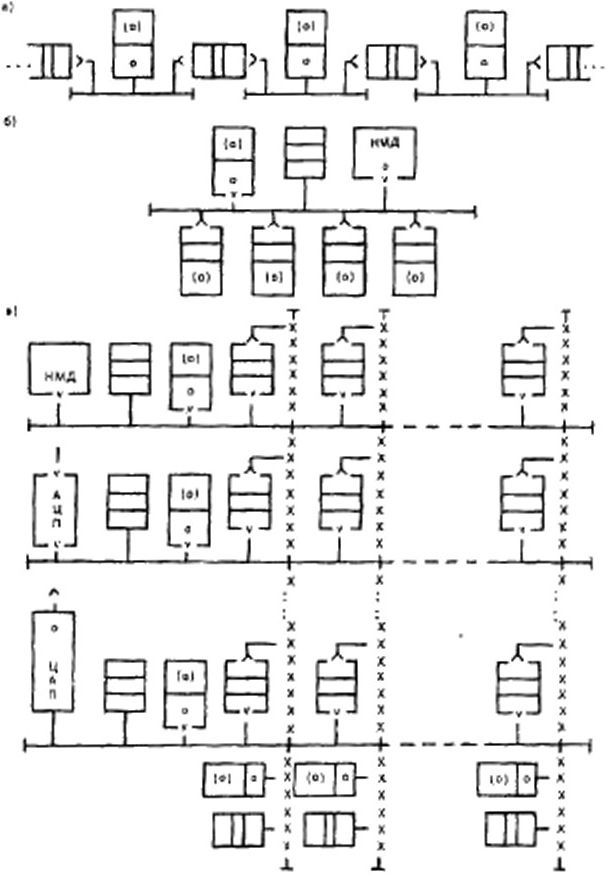

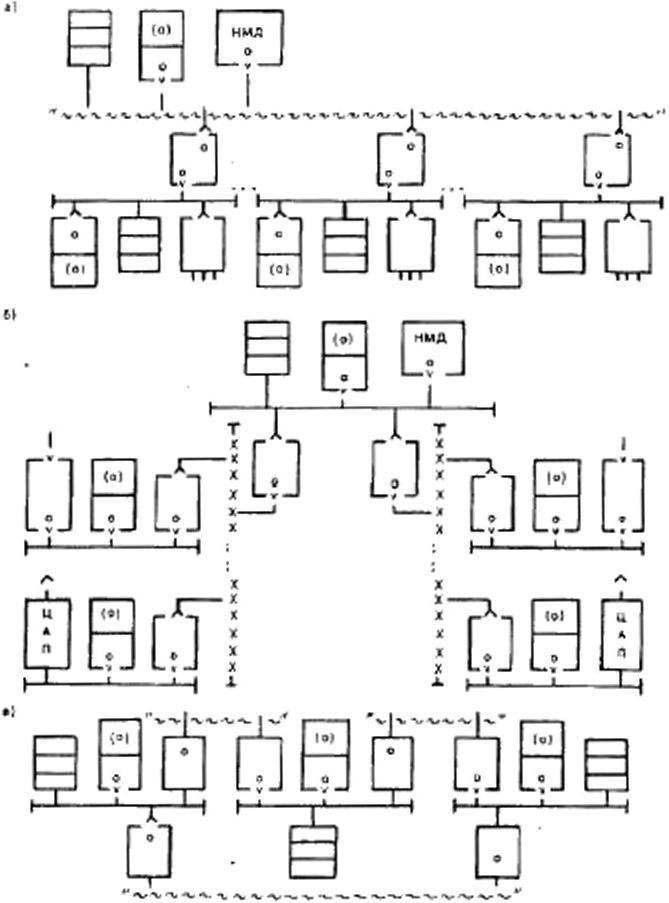

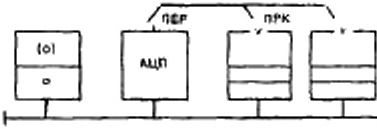

На рисунках А.1—Л.4 приложения А показаны примеры модулей, магистралей и систем, реализуемых с помощью интерфейса МСИ.

1.5 Магистраль интерфейса МСИ .может иметь различное функциональное назначение, например:

- магистраль процессора или его локальной памяти;

- магистраль ввода-вы вода;

• локальная или системная магистраль любого иерархического уровня системы.

Модуль интерфейса МСИ может иметь сложи кто иерархическую организацию, т. с. состоять из набора внутренних .магистралей и модулей.

2 ОБОЗНАЧЕНИЯ И СОКРАЩЕНИЯ | |

А АИ АР АЦП БА БЗ БР ВЛ ВБ ВТА ГГ га ГН го ГФ гч д дм дп ДР дт двз ЗА зд ЗИ | — адрес (* — произвольный); — адрес источника; — автономный режим; — аналого-цифровой преобразователь; — базовый адрес; — буферная зона; — биг резерва; — внутренний адрес; — величина блока данных; — вторичный адрес; — групповая готовность; — готовность задатчика; — готовность исполнителя к нечетной (разе цикла; — групповое обращение; — готовность фазы; — готовность исполнителя к четной фазе цикла; — данные; — доступ к магистрали; — доступ получен; — доступ разрешен; — доступ по требованию; — действующий задатчик; — задатчик автономный; — запрос доступа; — задатчик интерфейсный4. |

2

ГОСТ И SOW -9S

зм | — задатчик магистрали; |

30 | — запрос обслуживания; |

зп | — запись; |

зс | ~ задатчик связи; |

ЗФ | — задержка фазы; |

ЗБИ | — задатчик интерфейсный с буфером данных; |

ЗБС | — задатчик связи с буфером данных; |

зди | — задатчик дуплексный интерфейсный; |

ЗПА | — запись в автономном режиме; |

ИА | — исполнитель автономный; |

ИЗ | — идентификатор задатчика; |

ИИ | — исполнитель интерфейсный; |

им | — исполнитель магистрали; |

ин | — инициализация начальная; |

ип | — идентификатор-приоритет; |

ИС | — исполнитель связи; |

ИБС | — исполнитель связи с буфером данных; |

интерфейс МСИ — многоуровневый системный интерфейс;

К | — контроль; |

КЗ | — код завершения; |

КК | — код конца обращения; |

КМ | — код модуля; |

КН | — код начала обращения; |

КО | — коней обращения; |

КР | — команда в регистре управления; |

КЧ | — команда чтения; |

КП | — конец цикла; |

ДА | — логический адрес; |

М | — магистраль; |

МА | — модификатор адресного пространства; |

МД | — множественный доступ; |

МП | — микропроцессор, |

МР | ’— модификатор разрядности; |

мс | — модификатор связи; |

мт | — маршрутная таблица; |

МЛР | — младшие разряды; |

нд | — неготовность данных; |

ни | — нет импульсов, |

1-2Й)

3

ГОСТ J’ 50833-95

НП — неготовность питания;

НС — неготовность к связи;

НФ — недействительная фаза;

НМД — накопитель на магнитном диске;

03 — обслуживающий задатчик;

ОП — обслуживание передано;

ОР — обслуживание разрешено;

ОЗУ — оперативное запоминающее устройство;

П — приоритет;

ПА — позиционный адрес:

ПБ — пересылка в буфер;

ПД — пространство данных;

ПЗ — пользовательская зона;

ПП — приоритетное пространство;

ПР — пуск разрешен;

ПС — пространство связи;

ПЧ — проверка четности;

ПДИ — приоритет доступа к исполнителю;

ПЕР —передатчик;

ПРБ — прибор;

ПРЗ — претендующие задатчики;

ПРИ — претендующие исполнители;

ПРК — приемник;

РА — регистр (внутреннего) адреса;

РВ — регистр вектора прерываний;

РГ — регистр групповых маршрутов,

РД — регистр данных;

РЗ — регистр запросов;

РИ — регистр источника обслуживания;

РК — решетр конечного адреса;

РЛ — регистр логического адреса,

РМ — регистр масок;

РН — регистр начального (текущего) адреса;

РО — регистр ошибок;

РП — регистр приоритета;

PC — регистр счета (байтов);

FT — регистр таймера;

РУ — регистр управления;

СБ — сброс блока;

4

ГОСГ P 50833-95

CB C3 СИ CM co СГ1 Cll СРП CTP ТВ ТД T3 ТИ TK ТЛ | — синхроввод (сигналов с магистрали); — сквозная зона; — старт/исполнение; — связь с магистралью; — старт обращения; — синхроперс ключей ис (сигналов на магистрали); — старт цикла; — сохранение режима подчиненности; — старшие разряды; — время ввода (сигнала в модуль); — требование доступа к магистрали; — тайм-аут задатчика; — тайм-аут исполнителя; — тест/калибровка; — время распространения сигнала по всей длине линии ма-гистрали; |

TO ТП IT TU TTY ■ У УЗ ФВ ФД ФЗ ФО ФП ФС ФС1 ФС2 НАЛ ЦП ЧУ ЧБ чс ЧТ ШР шс | — требование обслуживания; — время переключения (выходных сигналов модуля); — период генератора тактирующих синхросигналов СП и СВ; — длительность цикла передачи данных; — терминал; — управление; — управляющая зона; — фаза входа (в арбитраж); — фаза (передачи) данных; — фаза завершения; — фаза обращения; — фаза получения (доступа) или передачи (30); — фаза сравнения (приоритетов); — фаза сравнения для старших разрядов кода приоритета; — фаза сравнения для младших разрядов кода приоритета; — цифроаналоговый преобразователь; — центральный процессор; — четность сигналов управления; — четность байтов; — число слоев памяти; — чтение; — шина с раздельными линиями А и Д, — шина с совмещенными линиями А и Д |

5

I OCI P 50833-95

J ОСНОВНЫЕ ХАРАКТЕРИСТИКИ

3.1 Интерфейс МСИ имеет:

- ускоренный поиск источников информации и программ сс обработки,

- распределенное программируемое управление магистралью;

- контроль, диагностирование и обеспечение резервирования магистрали и электронных модулей для построения отказоустойчивых систем.

3.2 Основным принципом функционирования систем с интерфейсом МСИ является принцип автономной и независимой работы каждой магистрали при способности к установлению необходимых связей между ними через связующие модели во всем объема системы.

3.3 Взаимодействия модуля, инициировавшего обмен в системе с интерфейсом МСИ, подразделяют на индивидуальные и групповые.

Все многообразие индивидуальных одноадресных взаимодействий выражается через комбинации двух элементарных взаимодействий:

- двух модулей через сопрягающую их магистраль;

- двух магистралей через сопрягающий их модуль.

Групповые взаимодействия включают в себя операции арбитража, запись данных в группу модулей, групповой опрос готовности модулей, двухадресные циклы передачи.

3.4 Протоколы магистрали интерфейса МСИ представляют собой единый иерархический ряд по уровню сложности; для выбора того или иного уровня используются модификаторы, что позволяет избежать избыточности в простых системах. По принципу передачи информации магистрали интерфейса МСИ могут быть параллельные и последовательные. Протокол последовательной магистрали является аналогом протокола параллельной магистрали, нос заменой параллельной передачи команд и данных иа последовательную.

3.5 В зависимости от режима работы и длины магистрали интерфейс МСИ обеспечивает частоту передачи данных, как указано в 5.1.2 (таблица 14).

4 СТРУКТУРА и СОСТАВ ЛОГИЧЕСКИХ СРЕДСТВ

4 1 При взаимодействии двух модулей через магистраль один из них должен выполнять функции задатчика — модуля, выдающего команды на магистраль, а другой - исполнителя — модуля, нслол-

6

няющего принимаемые с магистрали команды. Сопрягающий модуль, подключаемый к двум магистралям, может выполнять функции задатчика или исполнителя с каждой из сторон.

4.2 Основные функциональные типы исполнителей приведены в таблице I.

Таблица 1

Та депошителя | Нащюсияе |

ИЛ | Модуль, имеющий цифровую связь и получающий команды только от одной магистрали (МСИ) |

ИИ | Модуль, сопрягающий магистраль с внешним устройством; по отношению к устройству выступает хак источник команд, получая их с магистрали |

ИС | Сопрягающий модуль, который обеспечивает связь между двумя магистралями, принимая команды с обеих сторон |

Составной частью исполнителя является узел запроса обслуживания, с помощью которого исполнитель может обращаться к соответствующему источнику программ через магистраль. Исполнитель может иметь несколько однотипных каналов, например измерения или управления, а также может содержать буфер данных.

4.3 Основные функциональные типы задатчиков приведены в таблице 2.

Таблица 2

Тип ЯСПЧИКЛ | Пашкине |

За | Модуль, содержащий источник (буфер) команд и имеющий цифровую связь только с одной магистралью |

ЗИ | Модуль, осуществляющий сопряжение источника команд с ма-гисгрхчью и передающий от него команды иа магистраль |

зс | Сопрягающий модуль, который на одну передачу (блока) данных берет ла себя функции источники команд для обеих сопрягаемых магистралей |

7

ГОСТ I' 5081V 95

Задатчики последних двух типов являются сопрягающими задатчиками; они имеют узлы — исполнители получаемых команд. Задатчик может быть дуплексным, т. е. быть образованным сочетанием двух ориентированных в противоположные стороны задатчиков одного типа.

Составной частью задатчика многопроцессорной магистрали является узел запроса доступа, с помощью которого производится ар-битраж запросов доступа на магистраль. Задатчик может также иметь буфер данных, ’поделает его способным к работе в режиме автономной связи с одной из магистралей.

4.4 Магистрали, сопрягаемые через задатчики, могут иметь различную соподчиненность в соответствии с таблицей 3.

Таблица 3

В па с«т>хппн<и»<си | Опр<мемис |

Главная магистраль | Магистрат-, с которой поступают команды на сопрягающий задатчик |

Подчиненная магистраль | Магистраль, ив которую выставляет команды сопрягающий задатчик |

Если ЗИ дуплексный, роли магистралей могут меняться во времени местами.

4.5 Логические средства интерфейса МСИ позволяют резервировать магистрали (2-3-кратное резервирование).

4.6 По магистралям МСИ могут передаваться группы сигналов, приведенные в таблице 4.

Таблица 4

Кшивиоопвк ГРАНИН силой» | Н^шгииж |

Сигналы сии хронизация | Группа ситалов, используемая для тактирования и синхронизации обмена информацией |

Сипшы приоритета | Группа сигналов, необходимая для выявления наиболее приоритетных запросов доступа к магистрали, запросов обслуживания к выявления обслуживающих задатчиков - с наименьшим текущим приоритетом, а также для указания идентификатора задатчики или его приоритета доступа к исполнителю |

к

Окончание таблицы 4

ГОСТ Р 50833-95

Шижжжшис ipysnN отита | НоеКСИИе |

Сигналы уп-раМсния | Группа сигналов, необходимая для передачи команд, изменяющих состояние модулей |

Сигналы адре-00В-данных | Группа сигналов, служащая для установления связи с модулями и для Передачи информации |

Сигналы контроля | Группа сигналов, служащая для оперативной передачи информации об ошибках в работе магистрали и модулей |

Каждый стандартный сигнал обозначается двумя буквами, прсд-ставляюшими собой начальные буквы первых слов наименования сигнала. На параллельной магистрали сигналы передаются по одноименным линиям, а группам сигналов соответствуют одноименные группы линий, называемых шинами.

4.7 Сигналы синхронизации приведены в таблице 5.

Таблица 5

Опта | Наничснж | Кто аисшляет | Кто принимал |

СП | При появлении СП осуществляется переключение модулями сигналов на магистрали | Тактирующий модуль | Все модули магистрали |

св | При пояменни СВ осу-щесгкияегся ввод сигналов с магистрали в модули | Тактирующий модуль | Все модули магистрали |

гз | Синхросигнал, каждый перепад которого указывает на выставление команды и данных (записи) на магистраль и на го, что задатчик готов к выполнению команды | Действующий задатчик | Действующие исполнители |

ГН | Первый фронт его указывает на селекцию адреса исполнителем, каждый срез ГН подтверждает готовность исполнителя выполнить полученную команду | Один или труппа действующих исполнителей | Задатчик и группа действующих исполнителей |

9

ГОСТ I' 50833-9S

Окончание таблицы 5

Сиг №1 | Киихниме | Кто ихтмлот | Кт» ПЕГИМИ» ГТ |

гч | Каждый срез ГЧ также подтверждает готовность исполнителя выполнить полученную команду | Один или группадей-стпующих исполнителей. Задатчик в конце нечетного никла | Задатчик и группа действующих исполнителей |

гг | Срез ГГ показывает, что каждый из исполнителей проанализировал адрес и команду и 'по адресованная группа исполнителей готова к выполнению команды | Все модули магистрали, способные к групповым операциям | Все модули магистрали. способные к групповым операциям |

4.8 Сигналы приоритета приведены в таблице 6. Таблица 6

Сиг-KV1 | Нмюлтмиг | Кто МССТЭЩП | Кто приншевет |

ГД | Определяет участке задатчика в текущей очереди запросов доступа к магистрали | Задатчик, претендующий на доступ к магистрали | Действующий задатчик |

ГО | Определяет участие ис-пплиителя В текущей очереди на передачу вектора прерывания Либо является требованием опроса | Исполнитель, претендующий на обслуживание | Действующий задатчик |

ДМ | Сигнал, запрещающий арбитраж запросов доступа и занятие магистрали другими задатчиками | З&атчик, выигравший в предыдущем арбитраже ЗД | Вес претендующие модули |

дт | Выставляется как команда начала арбитража ЗД ИДИ 30 или как требование продления никла арбитража | Действующий задатчик в начале цикла арбитража, претендующие модули | Все модули, способные к групповым операциям |

10

Окончании т<ш>иии 6

ГОСТ P 50833-95

CWT* К VI | lt.oar«Hiu | Кп» •МПДОИП | К Гм нpi ихнит |

И1КЮ-И1107 | Линик, на которые, вы-стадляетея в цикле арбитража приоритет в унитарном коде; в Первом такте никла Передачи - идентификатор тактика я его приоритет доступа к исполнители* | Модули, участвующие в арбитраже; в первом такте цикла передачи — действу ющий задатчик | Модули, участвующие п арбитраже: нс пазникам. имеющие приоритетный дои туи |

•1.9 Сигналы управления приведены в таблице 7.

Т а б л и ц а 7

Сигни | Ивэажииг |

MCI. мег | Определяют коды: обращении, адресной* пространств.*, приращения внутреннего адреса, завершения цикла передачи |

МР1, МР2 | Модификаторы разрядности адреса и данных к питск передачи |

СО | На совмещенной шине АД указывает, что в зависимости о» к*мя пл MCI. МСЗ в следующей Фазе будет переда виться: втрнчиыи адрес. идентификатор-тцткоритет. адрес источника ИЛИ ве тчина (но-ка .чинных сообщения |

ко | На совмещенной шине Ail указывает. *по в следующей физе будут ПОрславапи-Я данные Одновременное надичие си гладов КО и СО на магистрали указы васг, чти линии адрес.* и данных раздельные и ч*п в следующей трозе будут передаваться внутренний адрес и данные |

311 | Запись в HcnamiHtu.-i|. |

СК | 1 рупнпрой сигнал в пределах магистрали. Одновременное наличие еншадои СБ и ДМ яшмек* командой нннн>кц|||затнт модулей магистрали |

Сигналы управления выставляются дсйстнуютпм копчиком. Они принимаются, в первой фаю обращения — всеми исполнителями магистрали, в остальных фатах никла передачи — действующими исполнителями

1 zw

II

ГОСТ Р 50833-95

4. J0 Сигналами А и Д являются сигналы АД00 — АД63

4.11 На параллельной магистрали сигналы Д на шине АД могут выставляться как параллельно с сигналами А (ШР), так и последовательно (ШС). Распределение сигналов А л Д для шины АД параллельной магистрали приведено в таблице 8.

Таблица 8

Сигом | lUu^iicnue |

АД00-М13 | ШС Адрес — в первой фазе обращения на линиях ДДОО—ДЦ-Ю: сигналы обращения или данных — в последующих (разах цикла передачи |

АД00- АД15 | ШР Адрес (.младшие разряды) — в фазе обращения, внутренний адрес — «фазах Передачи: младшая часть кода прйоршета — в фазе завершения при наличии команды арбитража: инверсный порядок старшинства разрядов |

АД16-АД31 М32- АД63 | Адрес (старшие разряды) — в фазе обращения; данные пли впуг ремний адрес - в следующих <|лззах Адрес (старшие разряды) — в фазе обращения; Данные — к tie-дующих фазах |

Сигналы на шину АД выставляются в первой фазе действующим задатчиком, как и в (^‘зах записи; в фазах чтения — действующим исполнителем. Они принимаются: в Перной фазе — всеми исполнителями магистрали, в остальных фазах записи — действующими исполнителями, а в фазах чтения — действующим задатчикам. На ШР н фазе завершения cut налы приоритета на линии А выставляются и принимаются претендующими задатчиками.

4.12 Сигналы контроля приведены в таблице 9.

Г л 6 а и я а 9

Сиг KU | Нящакмиг | Кю ВМьТ.*ЛХгТ | Кто црш1И>мег |

ни | Фрош сИ1Цж№ показывает. что через 10 мс действительные значения напряжения питания магистрали выйдут из установленных номинальных | Источи ик питания | Модуль чипклрилн |

12

Окинчакис тамицы 9

ГОСТ Р 50833 95

Сиг* 1Л! | IUwiwiiht | K1U 0НЯМЛЙ;Г | Кто ПрМННШГТ |

НС | Свилегельствуег. О селек ции обращения исполните .тем, ни ой его неспособности к выполнению полученной команды или занятости другими задатчиками или о неполучении доступа ЗИ к сопрягаемой магистрали. а также Г» необходимости прекратил, «иль | Действующий иснощппель | Действующий алятчик |

нд | Означает, что данные нс обработаны, не привыкни к необходимому формату, не буферизованы или нс проверены (например, ио четности). Сигналы НС н НД выставляются одновременно в случае обнаружения неисправимых ошибок п одной нт фаз: они блокируют текущий цикл | Действующий исполнитель | Действующий зала пик |

ЧУ | Четность сигналов управления | Действующий задатчик | Действующий исполнитель |

чш- ЧЬ32 | Признак четности сигналов на линиях: ИГКЮ-ИП07. АИ0О-/ХДО?. АД0«-АД13. АД16-АД23. ЛД24-АДЧ. лшг-лдзч. АД40-АД47. АЦ4Х-ЛД55. АД54>-.\Д63 | Действующий при 1 задатчик При 'П мсиашитсль | Действующий инки: истиси<ите.1ь спин. Жатик |

4 13 Каждый соединитель должен содержать группу позиционных выколов ПВО ПВ4, через которые в модуль постоянно вводится кол его позиции на магистрали.

4.14 Адресные пространства, которые может иметь модуль МСИ. перечислены в таблице 10

П

ГОСТ Р 50811- 95

Гибл и и и 10

Мр<1кх 1фОСТр1КСТ*> | Илхимт»: |

пп | ОГишеть общей системной памяти, выделенной для мшишасмой информации; рекомецдуется ДЛЯ хранения Программ |

пд | Область обшей системной памяти, выделенной лая регистров данных модуля |

ПС | Область общей системной памяти с унифицированным расположением регистров, с помощью которых осуществляются функции интерфейса: устаиоктсние связи, передача запросов, данных или изменение состояния модулей |

4.15 ПА модуля является непрерывный набор системных адресов, приписанных данному модулю в каждом из трех адресных пространств.

Внутренние адресные ЗОНЫ, которые может иметь модуль, перечислены в таблице 11.

Таблица И

Эяо | Ихшгкшге |

УЗ | Первые 61 ВА в ПС. предназначенные для раешхюженпя упнфп цириканиих регистров |

G3 | Вторые 64 Да я ПС, иреднлзилчемные ды peiHcipou приема и Передач it сообщений либо (старшая Полинина) для хранения паспортной информации о модуле |

113 | Зона от 128.то адреса до итейишны ВЛ. прелиа нтаченная для размещения регистров пользователя |

сз | «Окно» я старшей половине ВЛ 1ЫИ прямых (сквозных) обращений через узел интерфейса |

4.16 Унифицированные регистры зоны управления модуля интерфейса МСИ приведены в таблице 12.

14

Г ;i б л и на 12

ГОСГ Р 5ШЗ-95

Риппр | Ihwunw |

РУ | Основной регистр управления я статуса модуля; младший байт РУ управляет и индицирует режим работы модуля, второй — режимы святи, третий и четвертый — укатывают на способы обращения, режимы адресация и передачи данных |

РО | Содержит s унитарном коде, в младшем байте — указатели ошибок данных. во втором — ошибки святи, а в старших байтах — маски лих ошибок При записи Используйся для селективной! сброса регистров РУ |

РМ | Маскирует запросы внутренних узлов, запрещает выставление сигнала 30 модуля от замаскированных (в унитарном коде) разрядов регистра запросов, а также блокирует ттенис содержимого этих рлзрядов |

РЗ | Служит для хранения и опроса готовности внутренних узлов или модулей При записи используется для селективного сброса разрядов регистра масок |

РН | Содержит идентификатор программы, обслуживающей текущее прерывание |

РЛ | Содержит битовый адрес модуля |

п | Определяет программируемые интервады времени |

РГ | Содержит в унитарном коде идентификаторы групповых образце низ», команды ио которым модуль исполняет |

РН | Содержит в задатчике — косвенный адрес. но которому ин производит обращение; в исполнителе — полный млн внутренним косвенный адрес, но которому к нему производится обращение |

РК | Содержит последний адрес мнпжеснеишцо цикла передачи ИЛИ конечный адрес ешхянения |

РН | Содержит в диок'зиом коде приоритет доступа задатчика к магистрали или Приоритет доступа к исполнителю. э также идентификатор стандартною стизбшеиил |

РИ | Содержи! адрес обслужи (тающею иеючиикл протрамм которому зтодчинси модуль |

ГОСТ В 54)83.4- 95

(Ь:<1нчинм яш&юии 12

Р/икгр | Вачьтгеяис |

PC | Содержит: в задатчиках — величину оставшейся части передаваемого массива лаптах, к исполнителях — его переданную часть. Приме ч а н и е — В марлях связи и дуплексных модулях РУ PC — двойные; они относятся к каждой из сторон сопрягающих модулей |

РА | Программно недоступный решеф, б котором запоминается ВЛ. выставленный на мэптетрлпи |

СМ | Григгер связи с магистралью, программно недоступен |

4.17 Логически определенные интервалы вымени в интерфейсе МСИ приведены в таблице 13.

(' а б л и ц а 13

Пидов ККмемя | Зябкие |

II | Время распространения сигналов по всей длине линии маш играли |

и | Период генератора тактирующих синхросигналов СП и СВ |

111 | Время нере^1мчсния выходных сипплов модуля (при наличии еШ ПНуТреННСЙ ГОТОВНОСТИ) После1 Появления НИ МЗШс7рЖ1Н ТаКТИ-руюшеи» сипхросп гнала СП |

IB | Время, необходимое лы ввода сиенитов в модуль посте появления на магистрали тактирующего синхросигнала СВ |

п | Предельна допустимая дл1гпшыи>еп. ожидания доступа к мат-сараян перед началам цикля передачи |

TH | Предельно .тнуешмю! длительность ожидания доступа к модулю в цикх: передачи |

16

ГОС I И 50831-95

5 ПРОТОКОЛ АРБИТРАЖА НА ПАРАЛЛЕЛЬНОЙ МАГИСТРАЛИ

5 1 Тактирование магистрали. группой а я синхронизация

5 1.1 Шины параллельной магистрали должны функционировать по конвейерному принципу.

- выставление сигналов арбитража ЗД должно опережать выставление соответствующих им сигналов передачи данных на один цикл;

- выставление сигналов на шине управления должно опережать на одну фазу выставление соответствующих им сигналов на шине АД;

- сигналы диагностирования должны выставляться в следующей фазе после передачи А — Д.

На магистрали могут одновременно присутствовать сигналы двух циклов; передачи данных и арбитража.

5.1.2 Задатчик, установленный на 31-ю позицию магистрали, обязательно должен выполнять функции тактирующего модуля и непрерывно вырабатывать последовательность парафазных тактирующих сигналов СП, СВ. Рекомендуемое физическое положение тактирующего модуля — вблизи середины Магистрали.

Фронт (появление) СП обязательно должен служить синхросигналом переключения (если необходимо) сигналов, выводящихся из модулей на магистраль

Фронт СВ обязательно должен служить синхросигналом ввода сигналов с магистрали в модули

Период тактирующих синхросигналов СП и СВ на параллельной магистрж1и обязательно должен удовлетворять условию;

ТТ > 2max (TBmax; 2 ГЛ + ТПшах), (I)

где ТВмах и ТПмах — наибольшие ТВ и ТП модулей, подключенных к магистрали.

Длительность цикла передачи данных следующая;

ТЦ = 2ТТ — для единичного цикла;

ТЦ = ТТ — для множественного цикла

Таблица 14 показывает, юж рассчитывать частоты передачи данных по магистрали МСИ. При расчете принято значение скорости распространения сигнала но линии магистрали 10 нс/м (с учетом влияния паразитных емкостей модулей).

I?

I OCT P 50X33-95

I абли Ца 14

Хъшл МШН1 ПН г. ч | Часто?* огрыппи дошал по MPnur^uai МСИ И/ТЦ.1. МГн | |||||

ЕашичииО uml-i | Мы«ж?сп<миЫ1 ur.».i | |||||

ТВ-ТП КС | ||||||

4 | М | ми | * | л | 400 | |

0.5 | IS | 5 | Й.6 | 36 | 10 | 1.2 |

2.0 | 1,1 | 3.1 | 0,1 | II | 6,2 | 1.1 |

10.0 | 1.2 | 1 | 0,4 | 2.4 | 2 | ол |

5.1.3 Групповой синхроси!нал подтверждения ГГ должен обеспечивать переход к следующей фате цикла только после того, как все модули, участвовавшие в текущей фазе, завершили ее выполнение (независимо от их быстродействия). Признаком завершения фазы должен служить перепал, который образуется на линии групповой синхронизации при снятии самым медленным модулем сигнала синхронизации.

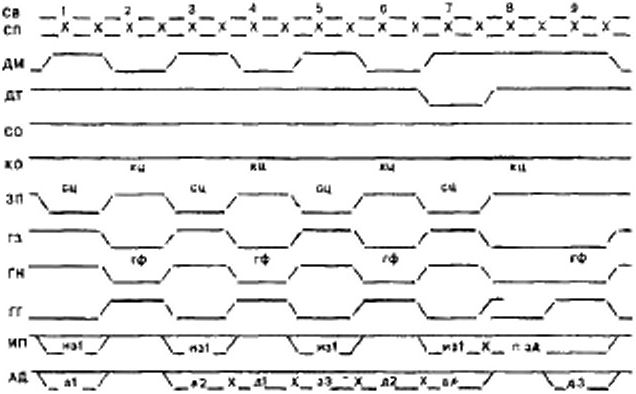

^«осуществления в множен пенном цикле передачи группового подтверждения на каждое переключение сигналов задатчика исполнители должны иметь два парафазных синхросигнала подтверждения ГН и ГЧ

Необходимость наличия линии ГГ в составе шины синхронизации определяется разработчиком системы.

5.2 Орган иза и и я ирпаритетной очереди запрос о в

5 2 1 Модуль с внутренним ЗД или 30, при наличии внутреннего разрешения | соответствен но ДР или ОР (ем таблицу 23)| в РУ. должен запрашивать доступ или обслуживание выставлением, соответственно. сигналов ГД или ТО

Арби Iраж запросов возможен по 63 у|ювням приоритета. Нулевые коды приоритета нс должны использоваться

5.2.2 Модули с высоким приоритетом (старшие 32-го уровня) могут выставлять сигналы требования арбитража в любом такте.

5.2.3 Модули с нормальным приоритетом (младший 31-го уровня} могут устанавливать текущую очередь запросов (по величине приоритета), гарантирующую выигрыш в арбитраже модулям с

ГОСТ Р 50X3.3 95

низким приоритетом при интенсивных обращениях к магистрали других задатчиков с нормальным приоритетом.

Признаком наличии очереди запросов должно являться наличие на магистрали требования арбитража — ТД или ТО.

Модуль с нормальным приоритетом должен выставлять свой сигнал требования, только зафиксировав отсутствие требовании на магистрали. Зафиксировав отсутствие других требований, модуль не должен снимать с магистрали свой синхросигнал IT до выставления своего требования на магистраль.

Претендующие, модуль с нормальным приоритетом, выставивший требование арбитража на магистраль, не должен снимать его до получения выигрыша и должен снять свое требование сразу после выигрыша арбитража.

Модули с нормальным приоритетом, которые нс смогли выставить своего требования, нс должны участвовать в циклах арбитража.

5.3 Протоколы циклов арбитража

5.3.1 Цикл арбитража может проводиться при отсутствии передачи данных или параллельно с циклом передачи данных, начинаясь в любой его нечетной фазе.

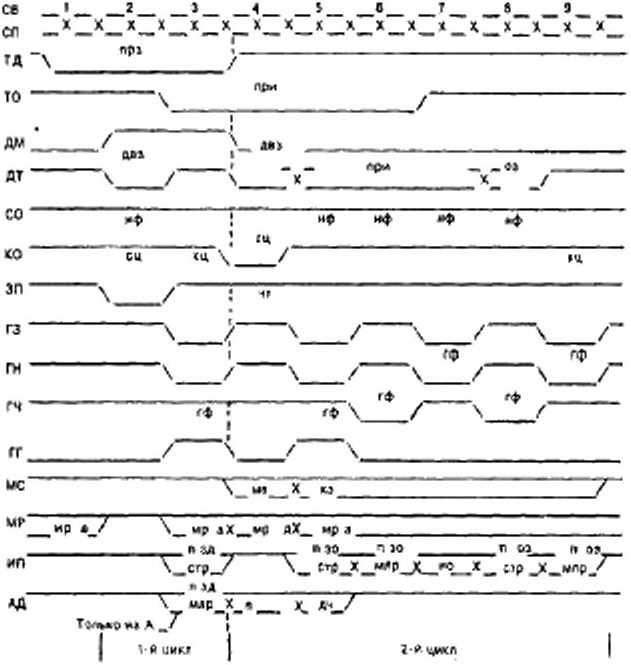

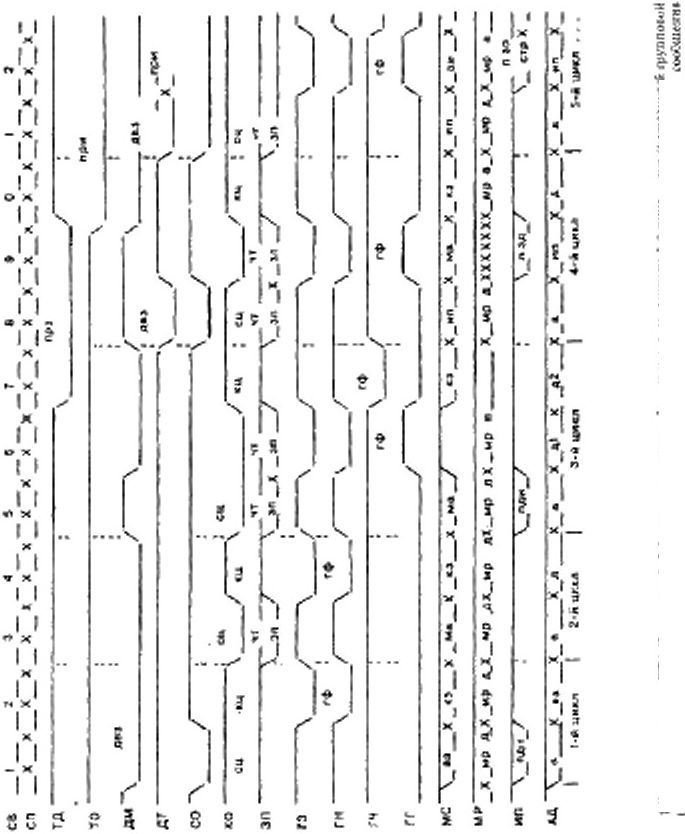

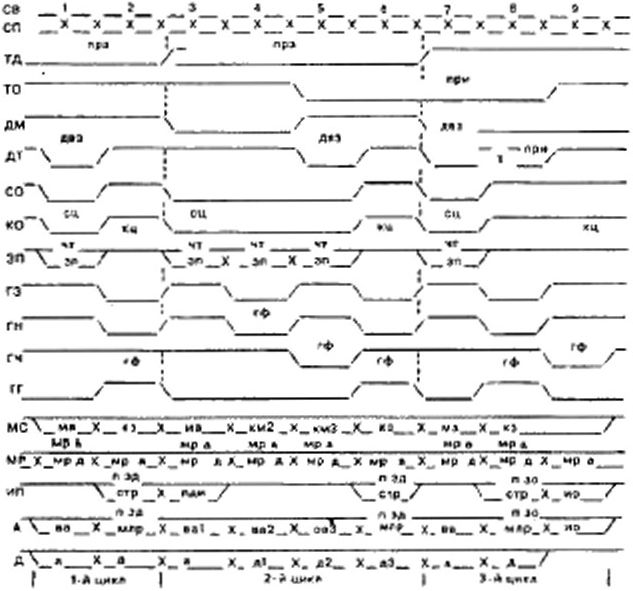

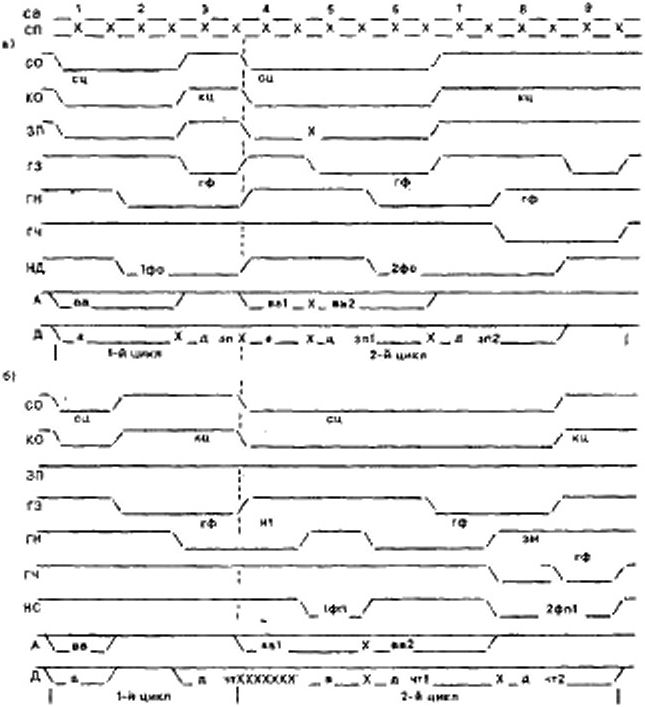

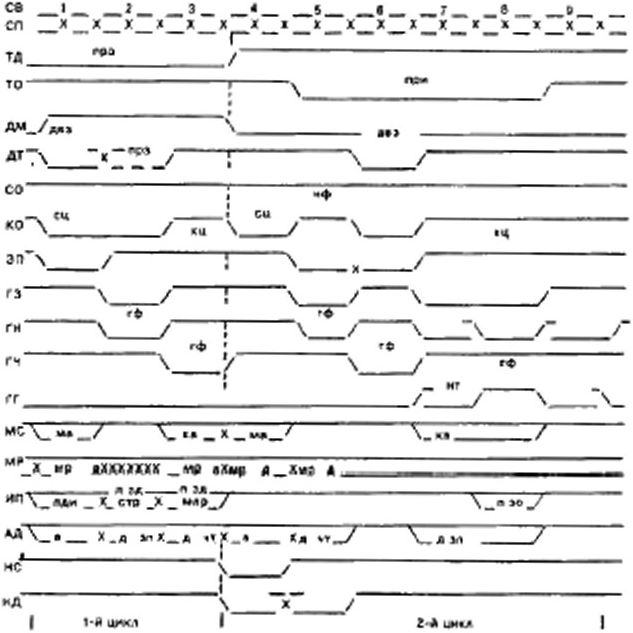

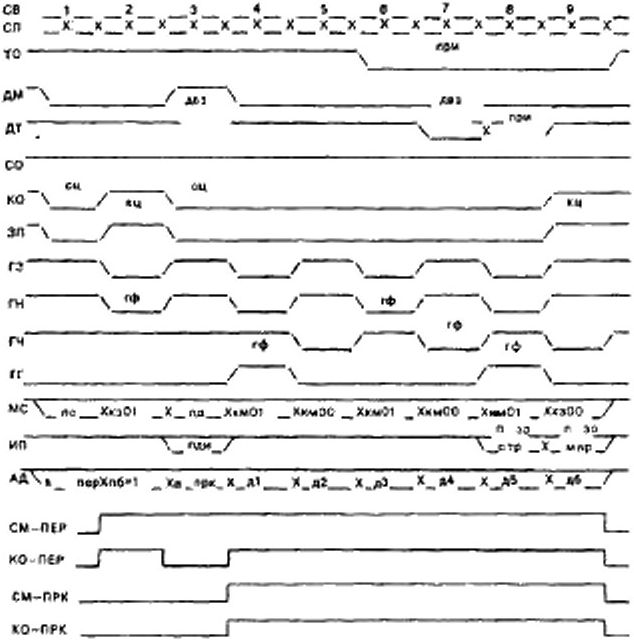

Протокол его проведения должен соответствовать: в первом случае — изображенному на рисунке Ь.1 приложения Б, а во втором случае — изображенному на рисунке Б.2 (4-й и 5-и никлы), рисунке Б Л (2-й и 3-й циклы), рисунках Б.5 и Б.6.

5.3.2 На ШР, а также на ШС, если .младшие три разряда 6 разрядного кода приоритета нулевые, цикл арбитража должен состоять из грех фаз: ФВ; ФС; ФП.

Ha IIIC. если три младших разряда кода приоритета в одном из модулей не нулевые, цикл арбитража должен содержать две (|юзы сравнения: ФС1; ФС2.

Фаза получения доступа может иметь нулевую и|>одолжитсльность.

5 3 3 ФВ должна начинаться действующим задатчиком н ответ на появление требования на шине арбитража Он должен выставить на магистраль следующую комбинацию сигналов:

- ДМ = О, ДТ = I — в цикле арбитража ЗД.

- ДМ = I, ДТ = I — в цикле арбитража 30.

Свободный (не проводящий цикл передачи) денсшующнй задатчик должен начать цикл арбитраж;) командой. СО - КО = 0. ЗП = I. — означающей, при нулевом ;шрссе. НФ цикла перначи данных.

к,м

19

ГОСТ J' SOW-95

Ha 11 IC претендующий модуль по команде начала арбитража должен выставить значение своих трех старших разрядов двоичного кода приоритета в виде сигналов в унитарном коде на одну из линий ИПОО — ИП07. Он должен также выставить на ШС сигнал ДТ, если содержимое его трех младших разрядов кода приоритета нс нулевое Нс ранее выставления указанных сигналов претендующий модуль должен выставить свой синхросигнал ГН и снять свой синхросигнал ГГ, подтверждающий его готовность к началу ФС.

Действующий задатчик, если им был начат фиктивный цикл передачи, должен по окончании первого такта снять свои сигнал ЗП и не ранее этого выставить своя синхросигналы ГЗ и ГН и снять свои синхросигнал ГГ.

Модули, ис претендующие на доступ к магистрали и имеющие выход на линию ГГ, должны в ФВ выставить синхросигнал ГН и снять свой синхросигнал ГГ.

ФВ должна заканчиваться, когда на магистрали снимется синхросигнал ГГ.

5.3.4 В первом такте ФС каждый претендующий .модуль должен проверить наличие сигналов на линиях ИН с номерами, большими чем номер гои линии, на которую он выставил сигнал приоритета Если таковые имеются, то претендующий модуль должен снять свой сигнал с линий ИПОО — ИП07 и нс выставлять ничего на эти линии до окончания арбитража.

Если нет сигналов ИП с более высоким приоритетом и управляющий сигнал ДТ = 0, то .модуль выиграл арбитраж, он должен установить разряд ДП ИЛИ ОП (таблица 23) в своем РУ (соответственно в циклах арбитража ЗД или 30). а также снять свой сигнал приоритета и снос требование с шины.

Если на шине имеется сигнал ДТ, то претендующие модули, выигравшие в первой фазе, должны продолжить арбитраж во второй ФС после снятия своих сигналов приоритета с общей линии ИП.

Модули, участвующие в арбитраже, должны нс ранее окончания своих действий вФС1 выставить синхросигнал ГГ и снять свои ГН. Эти же переключения синхросигналов должны выполнить все модули магистрали, способные к групповым операциям

Если в ФС1 выставлен ДТ, то претендующие модули должны одновременно со снятием ГН выставить своп синхросигнал ГЧ. действующий задатчик должен также снять свой синхросигнал ГЗ.

20

ГОС Г Р 50X11 95

Первая ФС должна заканчиваться, когда на магистрали восстановится значение синхросигнала ГГ и будет снят синхросигнал ГП

5.3.5 В ФС2, которая возможна только на ШС, сравнение кодон приоритетов должно производиться так же. как в ФС1, но для трех младших разрядов

Модуль, выигравший и первую и вторую ФС. должен в своем РУ и на магистрали произвести тс же действия, что и при одной ФС

Претендующие модули не ранее окончания своих действий во второй (разе сравнения должны снять свой синхросигнал 14 с магистрали.

Вторая ФС должна закончиться, когда на магистрали всеми моду-TIMH будет снят синхросигнал ГЧ.

5.3.6 При раздельных линиях Л и Д команда начала цикла арбитража должна выставляться за одну фазу до окончания четного цикла передачи (единичный никл относится к четным).

Унитарный код приоритета должен выставляться модулями на ШР нс только на линии ИП, но и на младшую часть линий АД. причем на последние он должен выставляться л инверсном порядке старшинства линии.

На Ш Р цикл арбитража должен содержать только одну ФС. т. с. претендующим модулям должно быть запрещено выставление сш • нала ДТ в ФВ

Сигналы синхронизации на ШР должны выставляться модулями гак же, как на ШС в соответствующих фазах.

5.3.7 Действующий задатчик должен контролировать продолжи-юльноить каждой ФВ и ФС; если она превышает значение ТИ, то он должен прервать выполнение текущего цикла, выставив СБ.

5.4 Протоколы циклон получения доступа

5.4.1 Циклы получения доступа к магистрали должны начинаться действующим задпчиком в случаях, когда он может ■ ступить доступ.

■ если он свободен, т. е. в его РУ разряд СП гем. таблицу 23) нулевой;

- если СП = [, но остановлен разряд множественного пост она (МД).

Во втором случае, после отпускания магистрали, задатчик должен сделать попытку се занятия снова в том же пикте получения доступа, который он начал, или в последующих циклах.

ГОС! В 50833-95

5.4.2 Поочередное предоставление доступа к магистрали

5.4.2 I Уступающий действующий задатчик, обнаружив наличие сигнала ТД на шине, должен найти претендующие задатчики. Поиск должен быть осуществлен поочередным опросом разряда ЗД в РУ (см. таблииу 23).

Претендующему задатчику, которому необходимо проставить доступ, действующий задатчик должен установить разряд «доступ получен» (далее — разряд ДП) в РУ (см. Таблицу 23). В фазе записи «I» н разряд ДП действующи!*! задатчик должен снять свой сигнал ДМ с магистрали.

Действующий задатчик может уступить доступ и без появления сигнала ТД на шине, установив разряд ДП любого задатчика магистрали.

5.4 2.2 Претендующий задатчик, которому установлен разряд ДП в регистре управления, должен снять свой сигнал ТД с магистрали, выставить свои модификаторы разрядности адреса на линии МР2, МР1 и сигнал ДМ на магистраль.

5.4.2.3 Для осуществления равномерного доступа поиск претендующих задатчиков может производиться тактирующим модулем, которому предварительно должно быть передано управление магистралью.

5.4 3 Арбитраж ЗД

5 4 3 1 Арбитраж ЗД должен производиться по протоколу 5.3, с дополнениями 5.4.3.2 — 5.4.3 4 и в соответствии и рисунком Б. 1 (1-й цикл), с рисунком Б.2 (4-й цикл), с рисунком Б.З (2-й цикл), с рисунком Б.5 (1-й никл) и с рисунком Б.6 (4-й цикл).

5.4.3.2 Одновременно с кодом приоритета доступа претендующие задатчики должны выставлять в ФС свои модификаторы разрядности адреса на линиях МР2, МР1.

Выигравший задатчик в последней ФС должен проверить совпадение кода на линиях МР2. МР1 со своей модификацией разрядности адреса.

ФП должна продолжаться до тех пор, пока уступающий действующий задатчик нс выставит комбинацию управляющих сигналов: СО = КО = ЗП = 0, — означающую конец цикла передачи, и пока кол на линиях МР2. MPI не совпадет со значением модификаторов разрядности адреса МРЛ2, МРЛ1 в РУ выигравшего задатчика. Оса •лих условия могут быть выполнены в ФС. тогда ФП будет иметь нулевую продолжительность

22

ГОСТ Р 50833-9$

5.4.33 Действующий задатчик, начав цикл арбитража ЗД, нс должен восстанавливать свой сигнал ДМ.

5.43.4 Тактирующий модуль должен проверять наличие на магистрали сигнала ДМ; если он отсутствует в интервале, большем чем ТЗ, то тактирующий модуль должен осуществить инициализацию магистрали и стать действующим задатчиком.

5.5 Поиск и арбитраж 30

5.5.1 Поочередный опрос испотчтелей

5.5.1.1 Действующий задатчик должен н определенном ею программой порядке производить поочередный опрос разрядов 30 (см. таблицу 23) в РУ исполнителей и найти тех, у которых он установлен.

5.5.1.2 Исполнителю, которому он сам нс в состоянии предоставить обслуживание, действующий задатчик может установить разряд ОП в РУ и передать идентификатор исполнителя 03.

5.5.1.3 Исполнитель, у которого нс выставлено требование обслуживания на магистраль, должен маскировать разряд .30 при ‘пении его РУ с магистрали.

5.5.2 Арбитраж- 30

5.5.2.1 Арбитраж 30 должен производиться ио протоколу 53, с дополнениями 5.5.2.2 — 5.5.2.5 и в соответствии с рисунком Б. I (2-й цикл), с рисунком Б.2 (5-й цикл), с рисунком БЗ (3-Й цикл), с рисунком Б.5 (2-й никл) и с рисунком Б.7.

5.5.2.2 При начавшемся арбитраже 30 действующий задатчик не должен переключать сигнал ДМ до снятия сигнала ДТ.

5.5.23 Если в ФС1 либо в ФС2 (на ШС) ни один из исполнителей не выставил сигнала ДТ, То ЦИКЛ арбитража 30 должен закончиться на этих фазах. Код приоритета 30 в этих случаях должен быть и идентификатором исполнителя. Однако, если в ФС2 имеется сигнал ДТ на магистрали, то это ДОЛЖНО означать, «по цикл арбитража 30 будет содержать четвертую фазу — ФП — передачи идентификатора обслуживания (вектора прерывания).

Идентификатор обслуживания должен выставляться в двоичном коде на линии ИПОО— ИП07 исполнителем, выигравшим арбитраж 30 в обеих ФС.

5.5.2 4 Вес задатчики, участвующие н цикле арбитража 30. должны считать идентификатор 30 с линии ИП в свой регистр — РВ.

5.5.2.5 Если содержимое разрядов адреса в РИ исполнителя нуле-

23

I (И Г Р МШ-95

нос. та он должен выставить ни шину арбитража н ФП сигнал ДТ. •шляющийся и это» (разе требованием начата цикла арбитража ОЗ

5 5.2.6 Исполнители пославший запрос, но нс получивший обслуживания в течение ТЗ. может повторно обратиться к шине арбитража с гем же 30.

5.5.3 Арбитраж: 03

5.5.3.1 Протокол цикла арбитража 03 должен соответствовать изо-буженному на рисунке Б. I приложения Б (2-й ЦИКЛ).

5.5.3.2 Цикл арбитража 03 должен проводиться непосредственно вслед та циклом арбпт]х>жа 30. если выигравший исполнитель вы-сгишл сигнал ДТ, означающий. что ему нс определен конкретный источник обслуживания.

Цикл арбитража 03 должен содержать ФВ, первую или вторую ФС; он должен содержать и ФП, если действующий задатчик в фате входа снял свой сигнал ДМ с магистрали.

5.5.3.3 В цикле арбитража 03 так же. как в цикле арбитража 30. должны участвовать те задатчики, у которых установлен разряд ОР в РУ.

03 должны йыстдмии. на шину нс прямое, а инверсное значение кода приоритета ЗД. приводящее к выигрышу пикта задатчиком с наименьшим приоритетом.

5.5 3.4 Уступающий действующий задатчик должен в ФВ 03 снять свой сигнал ДМ с магистрали.

5-5.3.5 Выигравший 03 должен установить разряд ОП в своем РУ.

Если на шине в Ф( сигнал ДМ отсутствует, то он должен также сстаношпьв своем РУ разряд ДП и по окончании «разы предоставления доступа стать действующим задатчиком.

5.5.3.6 Действующий 03 должен осуществить прерывание своих внутренних процедур и обработать приоритетный 30

5.5.3.7 Если на шине в ФС присутствует сигнал ДМ. то выиг-рявший 03 должен получить доступ к магистрали с помощью цикла арбитража ЗД.

5.5.4 Прерывание сообщением должно проводиться следующим обратом: модуль, нуждающийся в обслуживании и обладающий функциями задатчика, может занять магистраль по щютоколу арбитража ЗД. Заняв магистраль, он должен послать по адресу, находящемуся в его РИ. стандартное сообщение о 30. формат которого должен соответствовать указанному в таблице 26

ГОСТ Р 50833 95

6 ПРОТОКОЛ ЦИКЛА ПЕРЕДАЧИ ДАННЫХ НА ПАРАЛЛЕЛЬНОЙ МАГИСТРАЛИ

6.1 Фазы цикла передачи данных

6.1 I Цикл передачи данных должен содержать единичную или множественную ФО (передачи А и признаков обращения), в точен не которой устанавливается связь с одним исполнителем или группой исполнителей. Он может также содержать единичную или множественную ФД и должен содержать ФЗ.

6.1.2 Признаком отсутствия цикла передачи на магистрали должно являться отсутствие на ней управляющих сигналов (слева) и сигналов синхронизации (справа): СО. ГЗ, КО, ГЧ. ГН. ЗП, ДТ.

6.13 Командой начала цикла передачи должно являться появление одного из трех сигналов: СО. КО или ЗП — при отсутствии их нсех в предыдущем такте.

6.1 4 Признаком проведения цикла должно являться наличие на магистрали одного из сигналов: СО. КО, ЗП или ДТ.

6.1.5 Командой завершения никла должно являться снятие каждого из сигналов: СО, КО, ЗП — и для модулей, участвующих в групповых операциях цикла, также и сигнала ДТ при наличии хотя бы одного из них в предыдущем такте.

6.1 6 Первая фаза цикла передачи всегда должна быть фазой передачи адреса

Указывать на последующую ФО должно наличие ст нала СО в текущей фазе.

Указывать на последующую ФД должно наличке сигнала КО в текущей фазе.

6.1.7 Первая фаза цикла передачи данных всегда должна быть син-хроннои, т. с. занимать один такт магистрали. Продолжительность остальных фаз может быть от одного такта до ТИ.

6 2 М о д я ф и к а ц и и формата и разрядности ши н ы АД

6.2.1 Указателем UJC (в соответствии с рисунком Б.2) должно являться противоположное значение сигналов СО и КО в ФО и ФД.

Указателем ШР (в соответствии с рисунком Б 3) должно являться совпадающее (в том числе нулевое) значение сигналов СО и КО в ФО я ФД.

6.2.2 Разрядность выставленного А на магистрали может быть 16, 24. 32, 40 битов, а данных — Я, 16. 32. 64 бита.

ГОСТ И 50833-95

6.2.2.1 Управление и индикация разрядности А и Д должны проводиться полициям MPI и МР2 в соответствии с таблицей 15.

Г л В л н ц а 15

Лтенил | RlipUHIKIb Л КХ | л | Иитиыпмиг пиили AT | ||||

МП | MPI | ||||||

ШР | Л | вл | д | ||||

(1 | •J | X | 16 | 8 | 23-16 | 15-00 | 23-16 |

1) | I | X | Hi | 16 | 23-16 | 15-03 | 31-16 |

1 1) | 16 | 16 | 16 | 31-16 | 15-00 | 31-16 | |

1 1 | 16 | 24 | 32 | 39-24 | 23-00 | 63-32 | |

ШС | Полный адрес | д | |||||

0 | 0 | 16 | S | 15-00 | 07-00 | ||

(1 1 | 24 | 16 | 23-00 | 15-00 | |||

1 it | 32 | 32 | 31-00 | 31-00 | |||

1 1 | •Bl | 64 | 39-03 | 63-00 | |||

При LUC значения MPI и МР2 в ФО и ПД могут быть разными, т с. для каждой из четырех разрядностей А .может быть любая из четырех разрядностей Д

6.2.2.2 Указатели разрядности на линиях МР1 и МР2 должны выставляться на ШР с опережением на одну фазу в цикле.

На ШС они должны выставляться с дополнительным условием

- для А — перед началом никла передачи и в ФД;

- для Д — в последней ФО.

6.2.3 Формат выставляемых А и Д на линии АД должен соответствовать одному из указанных в таблице 14.

6.2.3.1 Если в разрядах старшего байга А содержатся нули, то

26

НИ I Р 5WW -95

задатчик должен почтить разрядность выставляемого А ни градацию — но линиям MPI и МР2

6.2.3.2 Исполнители с определенной разрядностью А нс должны иметь регистром и диапазоне А меньшей разрядности, т. с. старшин байт их А нс должен быть нулевым.

6.2.4 Разрядность селектора А в исполнителе обязательно должна соответствовать одной из четырех Ml’ А на .магистрали

Если МР адреса А. выставленного на магистрали, нс соответствует модификации А исполнителя, последний нс должен реагировать на обращение.

6.2-5 В ситуации, сели:

- разрядность Данных записи в исполнитель меньше разрядности его pel исТ]юв. но:

а) исполнитель нс имеет схем раздельной записи младших байтов или слов.

б) внутренняя позиция данных сдвинута, а исполнитель нс имеет де мул ьтиплс ксоров тал нс и.

- получена команда отдельного считывании старших байтов или слов, а исполнитель нс имеет мультиплексоров чтения, то исполнитель должен:

- нс записывать данные, если получена команда записи, и нс вы-стшиять Данные, если подучена команда чтения.

- ответить сигналом НД. свидетельствующим об ошибке в формате данных;

исполнителю также следует

- установить разряды РУООЧТ (чтения) и РО04 соответственно и РУ и 1’0.

6.3 Способы а д р с с а и и и

6.3 I Все регистры исполнителей, к которым имеется доступ со стороны системных магистралей, должны иметь логические адреса, однозначно определенные во всей системе.

6.3 2 Единицей адресации должен быть байт информации.

6 3.3 Обращение к адресным пространствам должно исстись и последней ФО цикла (при появлении КО) выставлением сшналон на линиях MCI и МСЗ в соответствии с таблицей 16

Ь-Ш-

21

ГОСТ В SOW-95

Табл и на 16

Энненик мех мет при иоэыы КО | Ацусжм лропрэнстм | Амхсаинп |

0 И | ПС | Логическая |

3 1 | пц | Логическая |

1 и | ПС | Позиционная |

1 1 | 1111 | Логическая |

6.3 4 Позиционная адресация

6.3.4.1 Максимальное количество модулей, подключаемых к параллельной магистрали, должно составлять 31. Отсчет номеров позиций должен начинаться с единицы и идти справа налево при виде со стороны соединителей.

Позиция модуля на магистржти должна определяться двоичным пятиразрядным кодом, вводимым через штырьки ПВО — ПВ4 соединителя магистрали.

6.3.4.2 При ПА обращение обязательно должно производиться к регистрам пространств;) связи исполнителя, т. е. в первой фазе ЦП должен присутствовать управляющий сигнал КО, а на линиях MCI и МС2 должен быть нулевой код

6.3.4.3 Полный ПА исполнителя должен состоять из кода позиции модуля, расположенного в старшем байте, и его ВА. расположенного в младших Липах. Формат ПА должен соответствовать приведенному в таблице 17

Гд блин и 17

Птим* Па | Гафин | Нииииног |

Старший байт | <17 - Об м <М - 00 | Кол основной ИЛИ резервной магистрали Указатель обращения к модулям своей магистрали Код позиции модуля |

Младшие банты | 31. 23. 15. 07 - 1)0 | ВА модуля либо латный ПА слелуннцсн магистрали по маршруту |

2Х

ГОСТ Г 5ШШ W

6.3.4 4 При ПА к модулям других магистралей действующий задатчик должен выставить и старшем байте в разряде 05 логический «0». а в разрядах 07 — 06 — код основной или резервной магистрали, к которой производится обращение.

В старшем и следующих ниже байтах и разрядах 04 — 00 должны содержаться ПА интерфейсных задатчиков, через которые последовательно осуществляется связь, т. с. физический маршрут связи.

В байте ПА исполнителя на конечной магистрали в 05-м разряде должна быть логическая «1», в следующих ниже байтах (сели хватает разрядности) должны содержаться ВА исполнителя.

6.3.4.5 Интерфейсный задатчик, находящийся на указанной в разрядах старшего байта позиции, должен передавать ПА с главной магистрали на подчиненную, если в 05-м разряде присутствует логи -чсский «0». Если в 05-м разряде находится логическая «I*, то ЗИ должен воспринимать обращение нс как транзитное, а как обращение к его внутренним регистрам.

6.3.4.6 Интерфейсный задатчик, пропуская позиционное обращение на подчиненную .магистраль, должен п коде на линиях МР2. МР1 понижать разрядность ПА на 1 байт

Если на ЗИ поступил 16-разряд ный адрес, то он должен содержать «I* в 05-м разряде старшего байта Если это условие нс выполнено, сопрягающий задатчик должен. нс исполняя полученной команды. ответить сигналом НС на обращение.

Сопрягающий задатчик, работающий с какой-либо модификацией разрядности IIA. должен работать и с модификациями меньшей разрядности Л пропускаемых обращений.

6 3 4 7 Если и разрядах 05 —07 старшего байта находятся нули, то ЗИ должен передать обращение всем магистралям, к которым он подключен своей управляющей стороной.

6.3 4 8 Исполнитель, при наличии ПА на магистрали и если в 05-м разряде старшего байта имеется логический «0». должен производить сравнение кода в разрядах 04 — 00 этого байта кодом на выводах ПВ4 — ПВО своего соединителя. В случае совпадения кодон он должен стать действующим исполнителем.

6.3.5 Логическая адресация

6.3.5 I Если ФО начинается с СО или с КО. но на линиях МС2. MCI имеется ненулевой код. то адресация к исполнителю обязательно должна быть по логическому идентификатору.

29

I OCT E 5ШЗ- 95

6,3.5.2 Полный ЛА исполнителя должен состоять из ЛА исполни-геля, расположенного и старших разрядах, и ВА исполнителя, расположенного в младших разрядах. Формат ЯЛ должен соответствовать приведенному и таблице 18.

I а 6 липа 13

РГф4П>1»Я1. | Kv impel >nGii1u« |

Потный Д.\ | 40. 32. 24. 16 |

НА модуля | N (младших! |

JIA модули | (44. 52. 24. 16) — N (старших! |

■'киический маршрут связи | M (старших) |

.'Ьпмческое фушпякн’ обращение и маршрут | О (ад 5 старших) |

6.3 5.3 Наименьший ЛА модуля должен являться его базовым адресом. по которому к нему Производится обращение.

Зона ВА модуля обязательно должна занимать целую страницу, т с содержать? в степени N байтов, хотя верхняя половина страницы может быть физически не занята полностью Вследствие этого базовый адрес модуля должен содержать нули в N-младших разрядах.

6.3 5.4 В модулях, нс имеющих внутренних модулей, распределение внутренних ЛА должно совпадать с распределением внутренних позиционных адресов.

В модулях, имеющих внутренние модули, старшая часть разрядов ВА должна являться ЛА внутреннего модуля, а младшая — его ВА.

6.3.5.5 Вазовый ЛА исполнителя должен храниться и младших разрядах РЛ.

При наличии полного ЛА на линиях АД магистрали исполнитель должен сравнить выставленный код А. га исключением N-младших разрядов, с имеющимся в РЛ. и в случае совпадения кодов он должен стать действующим исполнителем.

6 3.5.6 При прямой логической адресации к .модулям других ма-гпетрилей системы установление связи должно происходить ид основе анализа M-старших разрядов ЛА. задающих логический код маршрута связи

SO

ГОГГ 1' 51)8.1.1 95

Логические колы маршрутов спя л (должны храншьия к регистрах МТ в пространстве связи сопрягающих задатчиков. Для каждой lit четырех разрядностей ЛА в сопрягающем задатчике должна быть своя МТ Номер используемой МТ — МТО МТЗ должен определяться кодом разрядности А на линиях МР2, MPI Если стандартном зоны с ВЛ от 25 до 39 недостаточно для размешен ля МТ. то сс следует располагать в верхней части ПЗ адресов пространств;» связи

6.3.57 Селектор логического маршрута связи в сопрягающем задатчике должен выдавать сигнал пропускания обращения на подчиненную магистраль при любых сочетаниях нулей и единиц в разрядах ЛА» находящихся ниже М-старших маршрутных разрядов.

Значение М должно удовлетворять условию;

М < (40. 32, 24. 16) - N пй». (2)

где Л' — количество битов.

Рекомендуется значения М выбирать кратными четырем, а значения N — кратными восьми.

6.3.5.8 Рекомендуется, чтобы сопрягающий задатчик, работающин с какой-либо разрядностью ЛА. мог работать и с меньшими разрядностями ЛА пропускаемых обращений.

6.3.6 Групповая адресация

6.3.6.1 Признаком обращения к группе модулей либо ко всем модулям магистрали (либо по маршруту) должно являться, к соответствии с рисунком Б.2 (3-й цикл), снятие действующим задатчиком сигналов ДМ и ДТ в первой ФО.

6.3.6.2 Если н коде ПА. выставленного действующим ыдатчиком. в разрядах 00 — 04 старшего баша содержатся нули, то это должно означать, что обращение производится ко всем модулям данной ма гистрали.

Если и в 05-м разряде имеется логический «0», то Это означает, что обращение должно также передаваться интерфейсными задатчиками на их подчиненные магистрали (с понижением разрядности адреса на I байт).

6 3 6.3 Групповые логические обращения должны иметь код. оп-релслясмый G-старшими разрядами адреса. Адресуемый исполнитель группы должен распознавать этот код. В ннтер<реисном задатчике G-старших разрядов группового Л Л должны определять код группового маршрута.

п

гост Р 50Ш-95

6.3.6.4 Среди ЛА младшие I2S должны быть обязательно выделены для широковещательных групповых обращении ко веем модулям магистрали либо ко веем модулям нескольких магистралей вдоль широковещательного группового маршрута (имеющего нулевой код в старших G-разрядах). Разряды широковещательного ЛА (младшие 7 биток) должны задавать ВА модулей, к которым производится обращение.

6.3.6.5 РГ в исполнителе должен, в унитарном коде, задавать идеи иконка юры обращений, по которым он выполняет команды.

Интерфейсный задатчик, не имеющий буфера данных, нс должен сам исполнять групповые команды по маршрутам, заданным логической «I» в его РГ, а должен лишь передавать их на подчиненную магистраль.

6.4 Фазы цикла передачи данных

6 4 1 Разрешением к началу цикла передачи должны являться в задатчике наличие внутреннего сигнала ДП, наличие на магистрали его модификации разрядности адреса и отсутствие сигналов СО, КО. ЗП и ДТ.

6.4.2 Фаш обращения

6.4.2.1 Сигналы разрядности адреса на линиях МР2 и МР1 ШС АД должны выставляться задатчиком, как минимум, за один такт до начала первой ФО.

6.4.2.2 Первая ФО должна начинаться с выставления задатчиком на один такт комбинации сигналов управления: СО. КО, ЗП, МСЗ, MCI; кода адреса на линии: АД (39, 31, 23, 15) — 00; а также: на ШС — модификаторов разрядности вторичного адреса или данных, на ШР — модификаторов разрядности внутреннего адреса и данных — на линии МР2. MPI.

Если на магистрали в такте выставления адреса присутствует одни и: синхросигналов ГЗ, ГН или ГЧ (предыдущего цикла), го:

- задатчик обязательно должен, в соответствии с рисунком Б.З (2-й цикл), продлить фазу выставления адреса.

- исполнители обязательно должны нс проводить селекцию адреса.

Синхросигнал ГЗ должен выставляться задатчиком ни ранее вто рого такта, нс ранее снятия адреса исполнителя с магистрали и нс ранее выставления данных записи.

32

ГОСТ Р 5BH.3.3 95

6.4.23 Задатчик должен ждать получения ГН — синхросигнал подтверждения о распознавании обращения и выполнении команды одним из .модулей магистрали в течение ТИ.

При получении синхросигнал ГН связь при индивидуальной адресации должна считаться установленной.

6.4.2.4 При групповом обращении, протокол которого должен соответствовать рисунку Б.З (2-й цикл), после получения синхросигнала ГН, свидетельствующего об установлении связи с самым быстрым модулем в группе, задатчик должен дождаться снятия группового синхросигнала ГГ для подтверждения установления связи с самым медленным модулем.

6.4.2.5 В ситуации, если отсутствует подтверждение в интервале ТИ. задатчик должен установить разряды РУО 1 ЧТ и РО13 в РУ и РО; интерфейсному задатчику следует также установить в РУ разряд 30 на стороне главной магистрали. Затем задатчик должен снять свои сигналы с шины управления и АД. после чего нссостоявшиися цикл передачи завершается.

6.4.2 6 Сигналы разрядности адреса с линии МР2, МР1 обязательно должны приниматься исполнителем в каждом такте при отсутствии цикла на магистрали

Исполнитель в первом такте цикла обязательно должен считать с магистрали адрес и команду, сравнить адрес со своим собственным и, в случае совпадения кодов, должен установить разряд СП в своем РУ и внутренний триггер СМ в текущем цикле.

ВА должен быть записан исполнителем в РА (программно недоступен).

6.4.2.7 Если модуль выставил свои синхросигнал подтверждения, то он обязательно должен быть готов в такте появления встречного индивидуального или группового синхросигнала подтверждения передать или принять данные.

Адресованный исполнитель должен подготовиться к выполнению команды и ответить синхросигналом ГН. после чего он становится действующим исполнителем.

6.4.2.8 Исполнитель, имеющий вывод группового еинхросигнала ГГ. должен:

- при наличии управляющего сигнала ДМ и отсутствии ДТ удерживать сигнал на линии ГГ магистрали;

■ в такте группового обращения (ДМ * ДТ » 0) считать дцкге и

33

ГОСТ И 50831 95

команду, подготовиться к выполнению команды труп по ши о обращения. если код группы укачан вето РГ, выставить синхросигнал ГН и снять свой синхросшнал П с магистрали:

- при переходе к следующей фазе цикла выставить свои синхросигнал ГГ и снять спой синхросигнал ГН.

Выставление синхросигнала действующим исполнителем может опережать на несколько тактов снятие нм дополняющею синхросигнала. но оно обязательно не должно отставать от снятия ни на один такт.

6.4.2.9 Если разрядность адресной шины меньше разрядности полного ЛА, но достаточна для селекции исполнителем адреса модуля, го задатчик может выставить на магистраль в первой ФО комбинацию управляющих сигналов СО = I, КО - 0. МС2 = MCI = 0, — означающую незавершенность передачи адреса. Во торой (и последующих, сели необходимо) ФО задатчик должен, в соответствии с рисунком Б 2 (1-й цикл), выставлять младшие байты ВА исполнителя. При нескольких ФП ВА первыми должны передаваться старшие байты

6.4.2.10 Исполнители, имеющие схемы селекции и полного ЛА. 11 юлько ЛА модуля, должны работать с двумя модификациями разрядности адреса.

6.4.2.11 Интерфейсный задатчик, нс имеющий МТ. должен сравнивать адрес, выставленный в первом такте обращения, с содержимым своего РЛ. а вторичный адрес воспринимать как идентификатор модуля, к которому производится обращение.

6.4.2.12 Если одному из модулей необходимо приостановить цикл на магистрали, го он должен выставить одновременно оба синхросигнала I II и ГЧ

6.4.2.13 Если на магистрали однон|х?мснио присутствуют синхросигналы ГН и ГЧ, то счетчик ТИ в задатчике должен быть приостановлен. Во избежание «зависания* магистрали интервал одновременного выставления ГП и ГЧ должен быть ограничен значением ГЗ.

(1.4.2-14 Сопрягающий интерфейсный задатчик, обнаруживший, что имеющийся на главной магистрали адрес находится в его МТ. должен выставить на нес синки распознавания обращения — ГН Если ЗИ не имеет буфера данных, т. с. обеспечивает только непосредственную. единовременную связь с сопрягаемой машет-ралью (коммутацию каналов), го ему следует одновременно с ГН выс|а-

М

ГОСТ I* sow 95

вить синхросигнал ГЧ для приостановки цикла передачи ил главной магистрали на время подменяя доступа к сопрягаемой маги итрали.

Если за интервал времени 'ГЗ интерфейсным сдатчик нс получает доступа к сопрягаемой магистрали, то тогда он должен снять синхросигнал ГЧ с главной магистрали. В результате должен возобновиться счет времени TH в исходном .задатчике.

Синхросигнал ГЧ должен сниматься ЗИ и при получении доступа к подчиненной сопрягаемой магистрали.

6.4.2.15 Если на магистрали в течение интервала времени, большего чем ТЗтах, непрерывно присутствуют синхросигналы ГН и ГЧ, то тактирующий задатчик должен выработать СБ

6.4.3 Фаза передачи данных

6.4.3.1 В ФП данных на UJP задатчик должен выставлять на шину для исполнителя ВА данных следующей фазы.

При групповом обращении ВЛ может быть адрес модуля в группе. только этот модуль должен исполнять выставляемую команду.

Модификаторы разрядности и указатели адресного пространства должны на ШР задаваться также .тля каждой последующей фазы передачи данных.

6.4.3.2 Для задания ФП данных на ШС задатчик должен в последней ФО выставить сигналы СО = О, КО = I, модификаторы разрядности данных МР2. MPI и указатели адресного пространства МС2. MCI.

Нс позже выставления своего сигнала готовности к следующей фазе, т. с. переключения синхросигнала ГЗ. задатчик должен выставить модификаторы разрядности адреса (следующего цикла) па линии МР2. МРГ

6.4.3J Единичные и множественные, индивидуальные и групповые передачи данных должны провод 1нться к остальном единообразно на ШР и ШС.

6.4.3.4 В течение ТИ после выставления своего сигнала готовности (переключения ГЗ) задатчик должен н каждом такте П|ювс-рять появление сигнала готовности исполнителя:

- при споем ГЗ ~ 0 — снятия синхросигнала ГН с магистрали

- при своем ГЗ “Ч — снятии синхросигнала ГЧ с магистрали

В том же такте, в котором он обнаружил появление готовности исполнителя, задатчик обязательно должен принять данные чтения v магистрали, сели идет фаза чтения данных. Если идет фаза талией.

Л-JW

>5

ГОСТ Р 541833 95

сдатчик после обнаружения готовности исполнителя должен снять (или сменить) данные записи нс позднее очередного переключения своего синхросигнала ГЗ.

6.4.3.5 Если после смены состояния синхросигнала ГЗ задатчик в течение ТИ не получил сигнала подтверждения готовности исполнителя. то он должен завершить нссостоЯВШИЙел цикл передачи так же. как при отсутствии синхросигнала подтверждения в ФО

6.4.3.6 В цикле единичной передачи данных исполнитель нс должен выставлять синхросигнал ГЧ; этот синхросигнал должен быть выставлен совместно с ГН. только если есть необходимость в удержании состояния магистрали.

В цикле множественной передачи исполнитель, получив команду, должен подтвердить свою готовность к ее исполнению:

- при наличии синхросигнала ГЗ на магистрали в фазе получения команды — выставлением своего синхросигнала ГЧ и снятием своего синхросигнала ГН;

- при отсутствии ГЗ на магистрали н фазе получения команды — выставлением своего ГН и снятием своего ГЧ-

6.4.3.7 После выставления своего сигнала готовности исполнитель должен в каждом такте проверять появление сигнала ГЗ; в такте обнаружения ГЗ он обязательно должен принять с магистрали данные записи (если идет фаза записи) и команду для проведения следующей фазы.

6.4.3.8 Если исполнителем получена команда чтения, то он должен нс позже выставления своего сигнала готовности выставить данные чтения на магистраль. После обнаружения сигнала ГЗ он должен снять (или сменить) данные чтения нс позднее очередной смены состояния своих синхросигналов.

6.4.4 Фаза завершения

6.4.4.1 ФЗ должна использоваться для приведения к нулю всех сигналов модулей, участвующих в заканчивающемся цикле.

Командой перехода к ФЗ на шине АД должно являться снятие задатчиком каждого из сигналов СО, КО, ЗП. Командой перехода к ФЗ на шине приоритета должно являться снятие сигнала ДТ.

Последовательность снятия остальных сигналов в ФЗ должна зависеть от того, какой будет ФЗ в общем числе фаз в цикле:

- нечетной, тогда в предпоследней фазе ГЗ = I. ГН = I, ГЧ = 0;

- четной, тогда в предпоследней фазе ГЗ = 0. ГН =» 0, ГЧ ® 1.

36

ГОСТ Р 5083.1 95

6.4 4.2 Переходя к нечетной фазе завершения, перед снятием ГЗ задатчик должен выставить синхросигнал ГЧ

6.4.43 В четной ФЗ задатчик, при наличии готовности исполнителя, должен снять свои сигналы с шин управления и АД. а также синхросигнал ГЗ, после снятия которого на магистрам нс должно быть сигналов задатчика.

Исполнитель в четной ФЗ должен сбросить свой триггер СМ в цикле, снять свои данные чтения с шины АД и нс ранее этого снять свой синхросигнал ГН с магистрали.

6.4.4.4 В нечетной ФЗ задатчик, при наличии готовности исполнителя, должен снять свои сигналы с шин крапления и АД. а также свой синхросигнал ГЧ. после снятия которого на магистрали нс должно быть сигналов задатчика.

Исполнитель в нечетной ФЗ должен сбросить свой триггер связи СМ. снять свои данные чтения и. не ранее их, снять свой синхросигнал ГЧ с магистрали.

6.4.4.5 Если в команде перехода к ФЗ сигнал MCI * 0, то исполнитель должен сбросить в своем РУ разряд сохранения подчиненности магистрали; интерфейсный задатчик должен также освободить подчиненную магистраль.

6.4 4.6 Если исполнитель обнаружил ошибку в передаваемых и ФЗ данных, то он должен, выходя из ФЗ (одновременно со снятием синхросигнала ГН или ГЧ). выставить сигналы НД или НС. но только на один такт.

Задатчик должен фиксировать появление сигналов НС или НД на магистрали в любом из тактов ФЗ и обязательно в том такте, в котором он обнаружил снятие синхросигнала исполнителя (ГН или ГЧ) даже, если он сам сиял свои сигналы цикла с магистрали.

Наличие сигналов диагностирования на магистрали нс должно препятствовать началу следующего цикла.

6.4.5 На магист1>али должны быть выдержаны соответствующие соотношения сигналов.

6.4.5.1 На ШС модификаторы разрядности сигналов обращения и данных на линии МР2, MPI должны выставляться задатчиком одновременно с адресом модуля.

г.*

37

ГОСТ р 508.13-95

Модификаторы разрядности адреса должны быть выставлены на эти линии и предыдущем такте.

Модификаторы обращения и адресною пространства на линии МС2. MCI должны выставляться задатчиком одновременно с адресом.

6.4.5.2 Сигнал ЧУ должен выставляться задатчиком одновременно с сигналами управления.

Сигналы четности байтов данных — ЧБО — ЧБХ должны выставляться при записи задатчиком, а при чтении исполнителем — одновременно с данными.

6.4.53 Сигналы НС и НД ФО должны выставляться исполнителем в фазе, следующей за ФО. Сигналы НС и НД ФП данных должны выставляться исполнителем в фазе, следующей за этой ФП; если цикл исполнителем закончен, то они должны выставляться только на один такт.

6.43.4 Рекомендуемое значение ТИ:

ТИ = (10 - 100)ТТ (3)

Рекомендуемое значение ТЗ:

ТЗ = (100 - 1000ПТ. (4)

6.433 Время переключения модулями сигналов на магистрали должно быть определено при полной емкостной нагрузке линий магистрали Например, оно может быть измерено при работе передатчиков модуля на интегрирующую RC-цепочку:

- С “ 470 пФ для 21-местной магистрали:

■ R = 68 Ом. подключенному к источнику, плюс 3, 5 В.

6.43.6 Значение ТЛ протяженной либо ненагруженной магистрали может быть определено из расчета погонной задержки линий магистрали, равной 6 нс/м.

6 5 М о а ифи к а ц и и цикла пере д а ч и да н ных

63.1 Модификации цикла передачи данных должны определяться состоянием управляющих сигналов СО, КО. 311 в соответствии с таблицей 19

3S

I а б л и ц а 19

I ОС Г Р 50833-95

00 | Cikwiim КО | зп | Hxiokhik | |

1) | 0 | о | Окончание пики передачи на шине АД | |

0 | 0 | 1 | Недействительная фаза передачи. Зависят от ДМ. ДТ | |

0 | 1 | 0 | Конев обрашения, чтение данных | На ШС |

0 1 1 | Конец обращения, запись данных. | На ШС | ||

11 | |> | Чтение крушения | На ШС | |

■ о 1 | Запись обрашения. | На ШС | ||

। | 1 | п | Чтение данных. | На ШР |

1 | 1 | 1 | Запись данных. | На ШР |

6.5.2 Модификаторы связи с модулем

6.5.2.1 На ШС но второй или в последующих ФО передаваемая информация должна определяться значением модификаторов связи MCI, МС2 в соответствии с таблицей 20.

Табл к ц а 20

Сигижш мс: мел | TlHTICDK 1WHI», ил лимит ЛТ и ||«»о«у»Я1КЙ ФО 1И ШС |

п л | В ГЛ |

0 1 | ИП |

1 0 | ЛИ |

1 1 | вь |

Если в течение двух или более <1’0 сохраняется постоянным значение сигналов на линиях МСЗ, МО, это должно означать, что идет последовательная ие|»едача ВТА, ИП, АН или ВБ большей разрядности, чем указано на линиях МР2. МР1.

6.5 2 2 На ШР АД в фазах передачи данных сигналы на линиях МСЗ. MCI должны определять кол адресного пространства.

39

1 ОС I I’ SOW- 95

6.5 2.3 На ШС вФН данных постоянное (например, нуленос) значение кода на линиях МСЗ. MCI должно означать передачу по постоянному ВА.

Приращение числа, передаваемого полиниям МСЗ, MCI, на I. 2 или 3 в каждой фазе должно означать увеличение ВА исполнителя на I. 2 или 3 формата передаваемых данных.

6.5.2 4 В ФЗ сигналы, выставленные задатчиком на линиях МСЗ, MCI. образуют КЗ

Сигнал, выставленный на линию MCI. должен являться командой сохранения подчиненности:

- исполнителю — сохранить подчиненность главной магистрали.

- интерфейсному задатчику — сохранить доступ к подчиненной магистрали, т с удержать проложенный канал связи.

Сопрягающие модули в режиме сохранения подчиненности не должны исполнять команды с магистрали противоположной стороны.

Сигнал, выставленный на линию МСЗ, должен являться командой сохранения состояния исполнителя по завершении цикла и подготовки к следующему циклу. Если МС2 = 0. то исполнитель должен произвести текущий сброс и вернуться в начальное состояние.

6.5.3 Приоритетный доступ к модулю

6.5.3.1 Для обращения к модулям:

- имеющим узлы защиты от несанкционированного доступа,

- в приоритетном пространстве —

задатчик должен указать спой ИП.

Нулевой идентификатор должен означать свободный доступ к модулю.

6.5.3.2 На ШР ИП должен, в соответствии с рисунком Б 3 (2-ii цикл), выставляться на линиях ИП в ФО одновременно с адресом.

На ШС ИП должен выставляться:

- так же. как на ШР. в соответствии с рисунком Б.2 (1-и цикл), если магистраль содержит линии ИП;

- в отдельной ФО. в соответствии с рисунком Б.2 (4-й цикл) и с Таблицей 20.

6.5.3.3 Если задатчиком получен в фате приоритетного обращения диагностический сигнал НС = 1. то это должно означать, что выставленный им код приоритета нс совпадаете хранящимся в РП исполнителя.

4U

ГОСТ Г 50833-95

6.5.3.4 Модуль с приоритетным доступом, в разрядах РПГЮ — РП07 которого содержатся нули, должен отвечать на любое адресованное ему обращение и записывать его приоритет в указанные разряды своего РП.

6.5.3.5 Модуль с приоритетным доступом и отличными от нуля разрядами РПОО — РП07 в ФО должен сравнить код. находящийся в разрядах РПОО — РП07 его РП, с выставленным на линиях ИПОО — ИП07 (АДОО — АД07) магистрали и в случае совпадения кодов выполнить полученную команду.

6.5.3 6 Если в цикле приоритетного доступа нет совпадения кодов приоритета, то модуль нс должен выполнять полученную команду и должен ответить сигналом НС = I на обращение.

6.5.3.7 Модуль с приоритетным доступом должен производить сброс разрядов РПОО — РП07 при получении:

- КЗ МС2 = I, MCI = I;

- команды сброса или инициализации.

6.5.4 Повторная передача данных

6.5.4.1 Режим повторной передачи по постоянному адресу должен быть использован.

- при считывании массива данных неизвестной длины;

- при записи массива в буфер неизвестной длины.

6.5 4.2 Задатчик должен выполнять множественный цикл передачи по постоянному' ВА (сохраняя значения МС2 и MCI) до получения от исполнителя сигнала отсутствия данных (места в буфере) НД = I либо до достижения ограничения на максимальную длину массива — обнуления PC.

6.5.5 Автосканирование данных

6.5.5.1 Процедура автосканировання данных должна быть использована для последовательного поиска и сбора данных, случайным образом расположенных в различных модулях.

6.5.5.2 При автосканировании данных задатчик должен выполнять циклы множественной передачи с автоувеличением ВА. На ШС задатчик должен в ФП данных инкрементировать код на линиях МС2, MCI, а на 1ПР — производить автоувсличснис ВА исполнителя, если он получает от последнего сигналы НС = НД = 0 наличия данных

При получении сигнала отсутствия данных НД = I от исполнителя задатчик должен увеличить адрес исполнителя, г. е. обратиться к следующему модулю на магистрали.

41

КК Г Р SOW 95

6.5.5J При получении сигнала НС = 1 либо при исчерпании пре* зольной длины принимаемого массива (PC = 0), либо при достиже нии тинного в РК ограничения на конечный адрес модуля задатчик должен >авсршить процедуру автоскаинрования данных.

0.5.5.4 Интерфейсный задатчик должен выставлять в старшем Gaine данных на главную магистраль идентификатор (например, поэинн анныи номер) исполнителя, с которого он считал эти данные, а также идентификатор ВЛ исполнителя.

6.5.5.5 Для того чтобы процедура автоскан пропан пи данных нс нарушалась на адресах (или позициях), где модули отсутствуют, ин-зерфейсному задатчику следует устанавливать на главной магистрали состояние ожидания до получения ТИ на подчиненной магистра ли.

6.5.6 Двунаправленный цикл передачи данных

6.5.6.1 В цикле .множественной передачи задатчик может изменить в произвольной фазе направление передачи данных сменой состояния управляющего сигнала ЗП.

6.5.6.2 Пиклы «запнсь-модификация-чтенис (проверка)» должны проводиться в соответствии с рисунком Б.5(1-й цикл).

6.5.6.3 Циклы «’ггение-моднфикашш-эапись» должны проводиться в соответствии с рисунком Б.5 (2-ii цикл).

6.5.7 Расслоение памяти должно проводиться, как указано в 6.5.7.1 - 6.5.7.3.

6.5.7.1 Белл модуль памяти не успевает передавать (принимать) данные массива на каждый такт. ВА могут быть расслоены по нескольким модулям.

6.5.7 2 Модули с расслоением памяти должны, в соответствии с рисунком Ь.7 (2-п цикл), подключаться к магистрали групповым обращением и работать в фазах передачи поочередно, каждым на икон код модуля, выставленный задатчиком в предыдущем Такте фазы передачи данных на линиях МСЗ и МС1.

6.5 8 Разделяемый цикл передачи дачных

6.5 s | Если действующий задатчик начинает никл командой 111 - I. СО - КО - 0. то это должно означать, что передачи информации этого цикла во второй фазе нс будет, а будут передаваться сигналы другого цикла.

6.5.8 2 Модуль, к которому производится обращение в адресной факт разделенного цикла, называется буферным; он должен воспринимать сигнал ЗП в инверсном значении.

гос г г 5от -ж

6.5.8.3 Разделяемы»! цикл обязательно должен сопровождаться командой проведения групповых операций на магистрали.

6.5.8 4 Если в первой фазе разделяемого никла задатчик дал команду групповою обращения ДМ = ДТ - 0. то эти должно означать проведение им расщепленного цикла.

Протокол расщепленного цикла должен соответствовал, изображенному на рисунке Б 6.

Расщепленный цикл должен иметь идентификатор задатчика, выставляемый им в алленой фазе на линии ИП

6.5.8.5 Растепленный цикл передачи должен проводиться задатчиком, когда исполнитель не успевает сразу за адресной фазой выполнить ФП В расщепленном цикле должны выполняться только операции чтения данных.

Между адресной фазой и фазой передачи расщепленного никла может быть произвольное число тактов, н течение которых ни задатчик. ни исполнитель нс должны выставлять на магистраль сигналов этого цикла. Пауза может быть использована частями других расщепленных циклов, другими циклами либо другими задатчиками.

6.5.8 6 Исполнитель расщепленного цикла, распознав обращение к себе с определен»! ым идентификатором, нс должен выставлять ст -налов на магистраль до юх пор. пока он не обнаружит ла магистрали второго начала расщепленного цикла с тем же идентификатором; тогда он должен подключиться к магистрали и выполнить команду, полученную в первой адресной грате.

6.5.8.7 Задатчик, осуществив адресную фазу расщепленного цикла, может принять данные предыдущего расщепленного цикла, после чего выполнить адресную фазу следующего расщепленного цикла; затем он должен принять данные текущего растепленного цикла.

Если задатчику ист необходимости начинать следующий расщепленный никл, то он должен выполнить фиктивное начало biojkmo цикла с несуществующим адресом, но со своим идентификатором для того, чтобы принять данные исполнителя первого расщепленного никла.

В промежутках между частями расщепленного цикла задатчик может освободи» в магистраль.

6.5.8.8 Если в первой фазе разделяемого цикла шаатчикдал команду арбитража приоритетов 30 ДМ ~ ДТ - 1. ю это должно означать обращение к исполнителю с приоритетным запросом. Исполнитель, выигравши»! арбитраж приоритетов 30. в конце второй фазы должен подключиться к магистрали it нести обмен с буферным модулем.

43

ГОС! Г 5ШЗ-95

Буферным модулем может быть порт обмена самого задатчика.

6.5.9 Составной двухадресный цикл передачи данных

6.5.9.1 На магистрали так же, как при обращении к исполнителю с приоритетным запросом, может осуществляться пересылка информации непосредственно между двумя исполнителями, минуя задатчик. который должен лишь управлять прохождением цикла, выставляя адреса передающего и принимающего модулей.

6.5.9 2 Составной двухадресный цикл передачи должен, в соответствии с рисунком Б 7, состоять из двух связанных циклов:

- подключения буферного модуля к магистрали;

- обращения к передающему (принимающему) модулю.

6.5.9 3 Для подключения буферного модуля задатчик должен произвести запись «I* п разряд ПБ его РУ и закончить цикл с КЗ = 01. в результате чего буферный модуль не должен отключаться от магистрали.

6.5.9.4 Во втором цикле задатчик должен выполнить групповое обращение к передающему модулю с командой чтения либо к принимающему — с командой записи.

В фазе завершения задатчик должен выставить КЗ = 00, отключающий вес модули от магистрали.

6.5 9.5 Если в разряд ПБ РУ исполнителя записана «I», то он нс должен сбрасывать свой триггер СМ при КЗ » 01.

В фазе передачи данных буферный модуль должен выполнять действие с данными, обратное указываемому по линии ЗП

Буферный модуль должен завершать цикл связи с магистралью и сбрасывать разряд ПБ ТОЛЬКО при КЗ = 00.

6.5.9 6 В составном двухадресном цикле возможна поочередная работа с различными передающими и принимающими модулями, в частности автосканированис данных и одновременная работа с несколькими принимающими модулями в группе.

7 ПРОТОКОЛЫ ДИАГНОСТИРОВАНИЯ И ИНИЦИАЛИЗАЦИИ НА ПАРАЛЛЕЛЬНОЙ МАГИСТРАЛИ

7.1 Протокол шины контроля

Состав шины контроля определяется разработчиком системы.

7.1 I Сигнал НП должен быть обработан, как указано ниже.

7.1 I 1 Предупредительный сигнал НП должен выставляться на магистраль источником литания, он может быть выставлен в любой момент времени.

ГОСТ I’ 50833-95

7.1.1.2 При обнаружении сигнала НП модули должны выполнить предписанные им действия, направленные на сохранение своего статуса. связанные с проведением операций на магистрали, за время нс более 8 мс.