ГОСТ Р МЭК 821-2000

ГОСУДАРСТВЕННЫЙ СТАНДАРТ РОССИЙСКОЙ ФЕДЕРАЦИИ

МАГИСТРАЛЬ МИКРОПРОЦЕССОРНЫХ СИСТЕМ ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ РАЗРЯДНОСТЬЮ ОТ 1 ДО 4 БАЙТОВ (МАГИСТРАЛЬ VME)

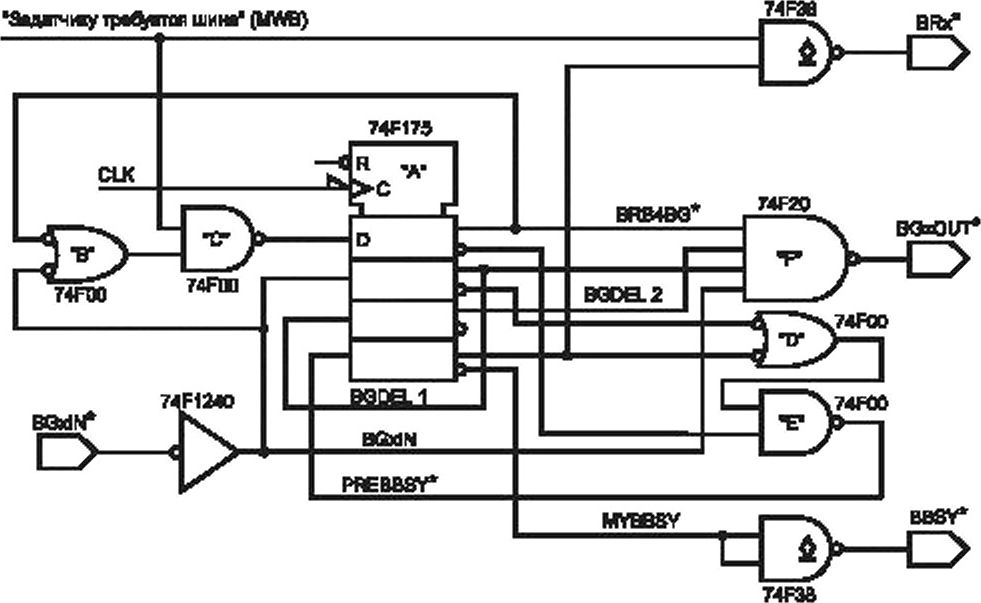

И мание официальное

БЗ 5-98/875

ГОССТАНДАРТ РОССИИ

Москва

ГОСТ Р МЭК 821-2000

Предисловие

1 РАЗРАБОТАН Нижегородским научно-исследовательским приборостроительным институтом «Кварц» (НН И ПИ «Кварц») и Научно-исследовательским институтом стандартизации и унификации (НИ ИСУ)

ВНЕСЕН Всероссийским научно-исследовательским институтом «Эталон»

2 ПРИНЯТ И ВВЕДЕН В ДЕЙСТВИЕ Постановлением Госстандарта России от 4апреля 2000 г. № 9()-ст

3 Настоящий стандарт содержит полный аутентичный текст международного стандарта МЭК821-91 «Магистраль микропроцессорных систем для обмена информацией разрядностью от 1 до 4 байтов ( Магистраль VMЕ )*

4 ВВЕДЕН ВПЕРВЫЕ

© ИИК Издательство стандартов. 2000

Настоящий стандарт не может быть полностью или частично воспроизведен, тиражирован и распространен в качестве официального издания без разрешения Госстандарта России

I!

ГОСТ Р МЭК 821-2000

Содержанке

I Область применения.......................1

I. I Назначение стандарта магистрали VMЕ................I

1.2 Элементы интерфейсной системы..................I

1.2.1 Основные определения....................1

1.2.1.1 Термины, используемые для описания механических конструкций магистрали VME.......................1

1.2.1.2 Термины, используемые для описания функциональной структуры магистрали VME...... 2

1.2.1.3 Типы циклов магистрали VME...............4

1.2.2 Основная структура магистрали VME...............5

1.3 Диаграммы, используемые в стандарте магистрали VME...........5

1.4 Терминология.......................7

1.4.1 Состояния сигнальных линий..................8

1.4.2 Использование звездочки ( * ).................8

1.5 Технические требования к протоколу.................8

1.5.1 Взаимосвязанные сигналы магистрали...............9

1.5.2 Широковещательные сигналы магистрали..............10

1.6 Примеры функционирования систем и пояснения.............10

2 Шина пересылки данных магистрали VME................10

2.1 Введение.........................10

2.2 Линии шины пересылки данных..................12

2.2.1 Линии адресации.....................12

2.2.2 Линии модификатора адреса..................13

2.2.3 Линии данных......................16

2.2.4 Линии управления шины пересылки данных.............16

2.2.4.1 Линия AS*.....................16

2.2.4.2 Линии DS0* и DSP..................16

2.2.4.3 Линия DTACK*...................17

2.2.4 4 Линия BERR*...................17

2.2 4.5 Линия WRITE*...................17

2.3 Функциональные блоки шины пересылки данных.............17

2.3.1 Задатчик.......................17

2.3.2 Исполнитель.......................19

2.3.3 Шинный таймер.....................20

2.3.4 Адресный монитор.....................21

2.3.5 Режимы адресации.....................22

2.3.6 Основные функциональные возможности пересылки данных........23

2.3.7 Возможности блочной пересылки................25

2.3.8 Функциональная возможность Чтение—Модификация—Запись........27

2.3.9 Возможности невыровненных пересылок..............28

2.3.10 Возможность использования цикла Только Адрес...........30

2.3.11 Взаимодействие между функциональными блоками шины пересылки данных . . 30

2.4 Типичные примеры работы....................31

2.4.1 Типичные циклы пересылки данных...............32

2.4.2 Конвейерная адресация...................36

2.5 Получение права на использование шины пересылки данных..........37

2.6 11равила и замечания по временном соотношениям сигналов шины пересылки данных . . 38

3 Шина арбитража.......................72

3.1 Основные принципы арбитража шины................72

3.1.1 Типы арбитража......................72

3.2 Линии шины арбитража.....................74

3.2.1 Линии запроса и предоставления шины...............75

3.2.2 Линия сигнала занятости шины (BBSY*)..............75

3.2.3 Линия очистки шины (BCLK*).................75

ill

ГОСТ Р МЭК 821-2000

3.3 Функциональные блоки.....................76

3.3.1 Арбитр.......................78

3.3.2 Запросчик.......................79

3.3.3 'Задатчик шины пересылки данных................80

3.3.3.1 Освобождение шины пересылки данных............80

3.3.3.2 Получение права на использование шины пересылки данных......81

З.З.З.З Дополнительная информация................81

3.4 Типичные примеры работы....................81

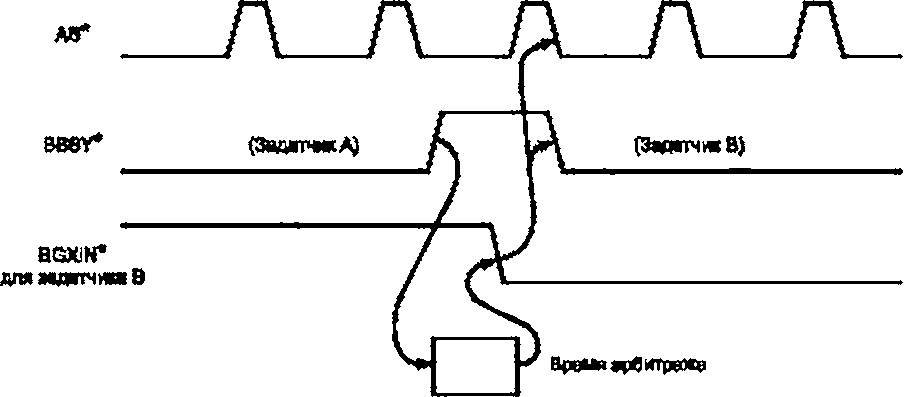

3.4.1 Арбитраж запросов шины двух различных уровней...........81

3.4.2 Арбитраж двух запросов шины на одной линии запроса..........85

3.5 Условия возникновения гонок между сигналами зап роса задатчика и предоставления шины арбитра.........................89

4 Шина приоритетных прерываний...................91

4.1 Введение.........................91

4.1.1 Систем ы п реры ван и й с од н и м обработч иком.............91

4.1.2 Распределенные системы прерываний...............91

4.2 Линии шины приоритетных прерываний................91

4.2.1 Линии запроса прерывания..................91

4.2.2 Линия подтверждения прерывания................93

4.2.3 Цепочка подтверждения прерывания (lACKINVIACKOUT*)........93

4.3 Функциональные блоки шины приоритетных прерываний. Общее описание.....94

4.3.1 Обработчики прерываний...................94

4.3.2 Прерыватель и его функции..................97

4.3.3 Формирователь цепочки подтверждения прерывания...........99

4.3.4 Возможности обработки прерывания...............100

4.3.5 Возможности запроса прерывания................100

4.3.6 Возможности пересылки информации статуса/идентификации........100

4.3.7 Возможность снятия запросов прерываний..............101

4.3.8 Взаимодействие между функциональными блоками шины приоритетных прерываний 103

4.4 Типичные примеры работы ....................104

4.4.1 Работа с одним обработчиком прерываний..............105

4.4.2 Работа распределенных систем прерывания.............105

4.4.2.1 Распределенные системы прерывания с семью обработчиками прерываний . 105

4.4.2.2 Распределенные системы прерывания с двумя—шестью обработчиками . .105

4.4.3 Типичный пример работы системы прерывания с одним обработчиком .... 105

4.4.4 Пример назначения приоритетов двум прерываниям в распределенной системе прерывания ........................110

4.5 Условия возникновения гонок...................112

4.6 Правила и замечания по временным соотношениям сигналов шины приоритетных прерываний ..........................ИЗ

5 Служебная шина.......................132

5.1 Введение.........................132

5.2 Сигнальные линии служебной шины.................132

5.3 Функциональные блоки служебной шины...............132

5.3.1 Формирователь системного тактового сип<ала.............132

5.3.2 Формирователь тактового сигнала последовательной магистрали.......132

5.3.3 Блок контроля питания...................132

5.4 Инициализация и диагностика системы................135

5.5 Контакты питания......................137

5.6 Резервная линия.......................138

6 Электрические характеристики магистрали VM Е..............138

6.1 Введение.........................138

6.2 Распределение питания.....................139

6.2.1 Технические требования к источникам питания постоянного тока.......139

6.2.2 Электрические параметры гнездовых и штыревых соединителей.......139

IV

ГОСТ РМЭК 821-2000

6.3 Электрические характеристики сигналов................140

6.4 Требования к характеристикам формирователей и приемников сигналов магистрали ... 140

6.4.1 Определение типов формирователей магистрали............141

6.4.2 Требования к характеристикам формирователей и нагрузок для всех линий . . . .141

6.4.2.1 Требования к характеристикам формирователей с тремя состояниями и нагрузок для сильноточных линий AS*. DS0*, DSI*..........141

6.4.2.2 Требования к характеристикам формирователей с тремя состояниями и нагрузок для стандартных л ин ий АО 1-АЗ I, D00-D31, АМО-АМ 5,1АСК*, LWORD*. WRITE*......................142

6.4.2.3 Требования к характеристикам формирователей с двумя состояниями и нагрузок для сильноточных линий SERCLK. SYSCLK. BCLR*......142

6.4.2.4 Требования к характеристикам формирователей с двумя состояниями и нагрузок для стандартных линий BG()OUT*-BG3OUT*/BG0IN*-BG3IN*.

1ACK0UT71ACKIN-..................143

6.4.2.5 Требования к характеристикам формирователей с открытым коллектором и нагрузок для линий BIW-BR3*, BBSY*, IRQP-1RQ7*, DTACK*. BERR*.

SYSFA1L", SYS RESET*. AC FAIL* и IACK*..........143

6.5 Межсоединения сигнальных линий объединительной платы..........144

6.5.1 Оконечные нагрузки....................144

6.5.2 Волновое сопротивление..................145

6.5.3 Дополнительные сведения...................147

6.6 Сигналы, определяемые пользователем................148

6.7 Формирователи и оконечные нагрузки сигнальных линий...........148

7 Требования к механическим конструкциям................149

7.1 Введение.........................149

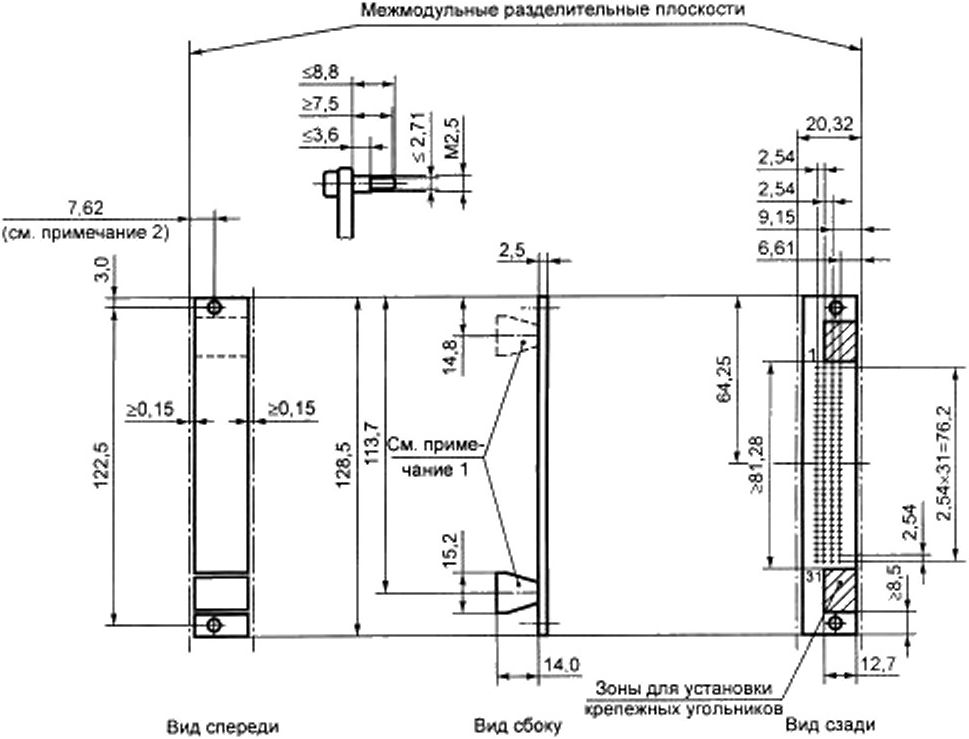

7.2 Печатные платы модулей магистрали VME...............150

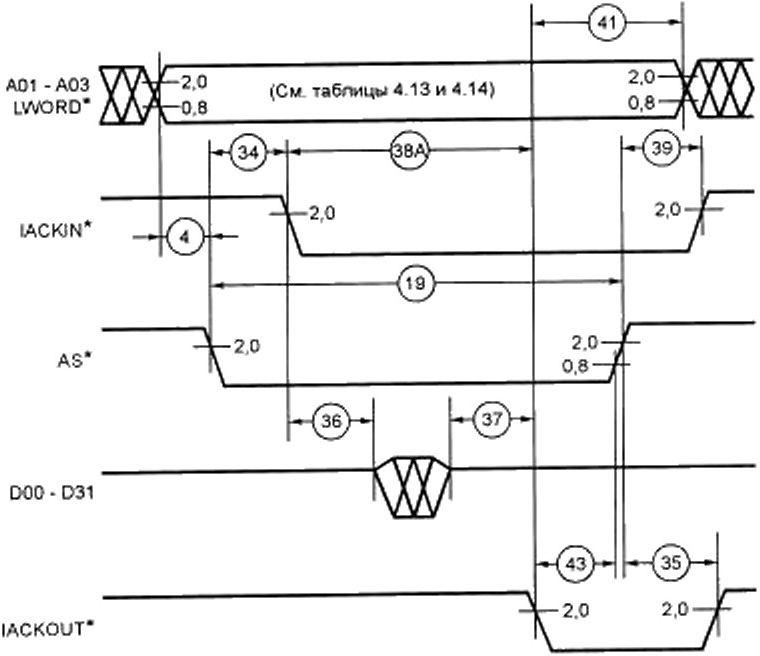

7.2.1 Платы модулей одинарной высоты................150

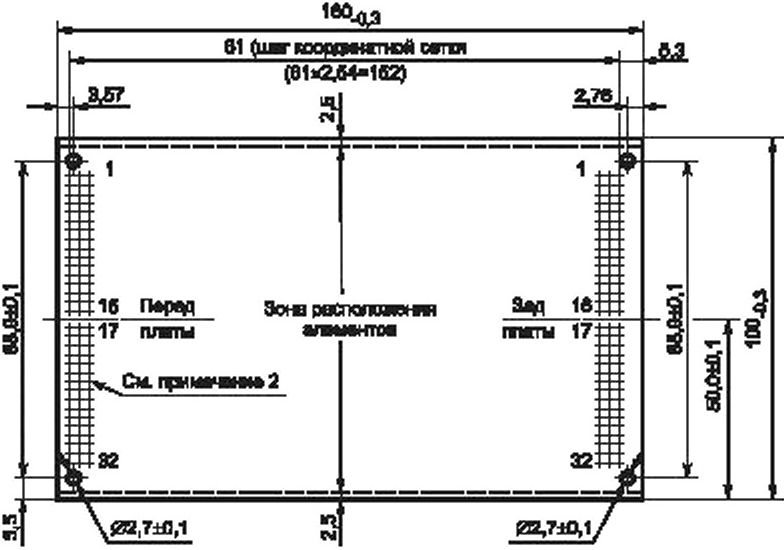

7.2.2 Платы модулей двойной высоты.................151

7.2.3 Соединители печатных плат модулей...............151

7.2.4 Компоновка модуля....................151

7.2.5 Ширина модуля......................152

7.2.6 Коробление печатной платы модуля, длина выводов и высота элементов . . . .152

7.3 Передние панели.......................152

7.3.1 Рукоятки.......................152

7.3.2 Крепление передних панелей..................153

7.3.3 Размеры передней панели...................153

7.3.4 Панели-заглушки.....................153

7.3.5 Эжекторы и инжекторы модулей.................154

7.4 Объединительные платы.....................154

7.4.1 Требования к размерам объединительной платы............154

7.4.2 Оконечные нагрузки сигнальных линий..............155

7.5 Сборка каркасов магистрали V.ME..................155

7.5.1 Каркасы и ширина гнезд...................155

7.5.2 Размеры каркаса.....................155

7.6 Соединители объединительных плат и модулей магистрам VME.........175

7.6.1 Распределение сигналов по контактам соединителей J1/PI.........175

7.6.2 Распределение сигналов по контактам соединителей J2/P2.........175

Приложение Л Словарь специальных терминов, используемых для описания магистрали VME . 177

Приложение В Описание сигналов на выходах соединителей магистрали VME......180

Приложение С Использование линий SERCLK и SERDAT*...........183

Приложение D Мегастабильность и ресинхронизация..............185

Приложение Е Допустимые поднаборы возможностей.............198

Приложение F Библиография.....................203

V

ГОСТ Р МЭК 821-2000

I крсчень рисунков

1.1 Элементы системы, определенные настоящим сгиизартом..........2

1.2 Функциональные блоки и шины, определяемые настоящим стандартом......6

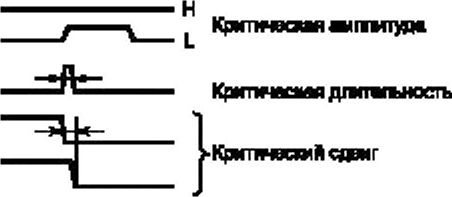

1.3 Система обозначений, применяемых при изображении временной диаграммы сигналов . . 9

2.1 Схема взаимодействия шины пересылки данных с функциональными блоками ... 11

2.2 Схема взаимодействия задатчика с магистралью............18

2.3 Схема взаимодействия исполнителя с магистралью............19

2.4 Схема взаимодействия шинного таймера с магистралью...........20

2.5 Схема взаимодействия адресного монитора с магистралью..........21

2.6 Четыре способа размещения в памяти 32 разрядов данных..........28

2.7 Четыре способа размещения в памяти 16 разрядов данных..........29

2.8 Пример однобайтового цикла считывания..............32

2.9 Пример двухбайтового цикла записи................34

2.10 Пример четырехбайтового цикла записи..............35

2.11 Последовательность смены задатчика шины пересылки данных........37

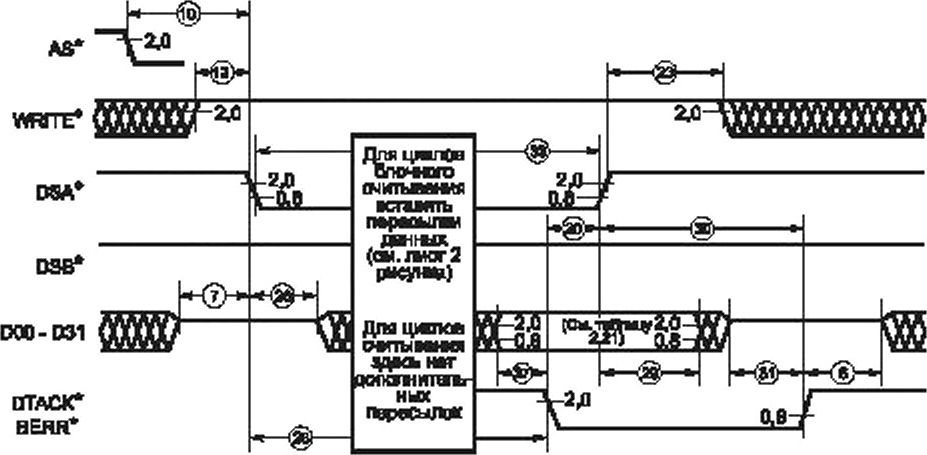

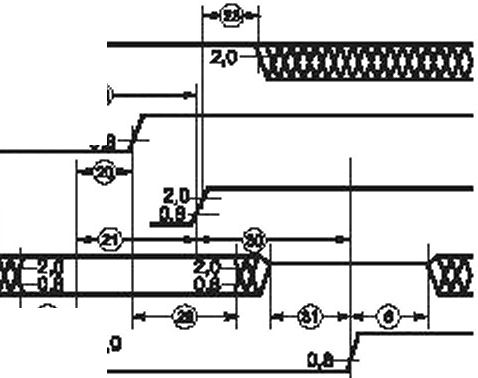

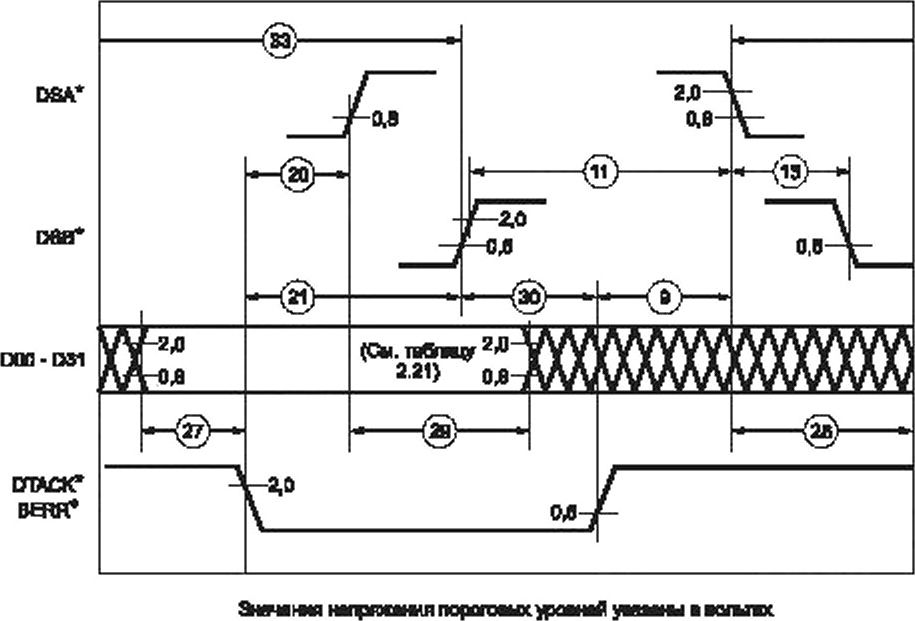

2.12 Временная диаграмма широковещательной пересылки адреса. ЗАДАТЧИК. ИСПОЛНИТЕЛЬ и АДРЕСНЫЙ МОНИТОР (Все типы циклов)............53

2.13 Временная диаграмма широковещательной пересылки адреса. ЗАДАТЧИК, ИСПОЛНИТЕЛЬ и АДРЕСН Ы Й МОН И ГОР. (I кресылка одного четного байта; пересылка одного нечетного байта; двухбайтовые пересылки; четырехбайтовые пересылки: невыровненные пересылки) 54

2.14 Временная диаграмма широковещательной пересылки адреса. ЗАДАТЧИК, ИСПОЛНИТЕЛЬ и .АДРЕСНЫЙ МОНИТОР. (Однобайтовые блочные пересылки; двухбайтовые блочные пе-ресылки; четырехбайтовые блочные пересылки)............55

2.15 Временная диаграмма широковещательной пересылки адреса. ЗАДАТЧИК. ИСПОЛНИТЕЛЬ и.АДРЕСНЫЙ МОНИТОР. (Однобайтовые циклы Чтение Модификация—Запись;двухбайтовые циклы Чтение Модификация ’Запись; четырехбайтовые пикты Чтение—Модификация—Запись) ......................56

2.16 Временная диаграмма пересылки данных. ЗАДАТЧИК, ИСПОЛНИТЕЛЬ и АДРЕСНЫЙ МОНИТОР. (Считывание байта (0); считывание байга (1); считывание байта (2); считывание байта (3); считывание байтов (0—2); считывание байтов (1—3); однобайтовое блочное считывание).......................57

2.17 Временная диаграмма пересыпки данных. ЗАДАТЧИК, ИСПОЛНИТЕЛЬ и /АДРЕСНЫЙ МОНИТОР. (Считывание байтов (0—1); считывание байтов (2—3); считывание байтов (0—3); считывание байтов (1-2); двухбайтовое блочное считывание; четырехбайтовое блочное считывание) .......................59

2.18 Временная диаграмма пересыпки данных. ЗАДАТЧИК. ИСПОЛНИТЕЛЬ и АДРЕСНЫЙ МОН ИТОР. ( Запись байта (0); запись байта (1); запись байта (2); запись байта (3); запись байтов (0—2); запись байтов (1 — 3); однобайтовая блочная запись).......61

2.19 Временная диаграмма пересылки данных. ЗАДАТЧИК. ИСПОЛНИТЕЛЬ и АДРЕСНЫЙ МОНИТОР. (Запись байтов (0—1); запись байтов (2—3); запись байтов (0—3); запись байтов (1— 2); двухбайтовая блочная запись; четырехбайтовая блочная запись) .... 63

2.20 Временная диаграмма пересыпки данных. ЗАДАТЧИК, ИСПОЛНИТЕЛЬ и АДРЕСНЫЙ МОНИТОР. (Однобайтовый пикт Чтение—Модификация—Запись)......„-65

2.21 Временная диаграмма пересыпки данных. ЗАДАТЧ И К. ИСПОЛ Н ИТЕЛ Ь и АДРЕСНЫ Й МОНИТОР. (Двухбайтовые циклы Чтение—Модификация—Запись; четырехбайтовые пикты Чтение—Модификация—Запись)..................66

2.22 Временная диаграмма адресного строба между циклами...........67

2.23 Временная диаграмма стробов данных между пиктами. За циклом, в котором оба строба данных устанавливаются низкими, следует цикл, в котором один или оба строба устанавливаются низкими.......................68

2.24 Временная диаграмма стробов данных между циклами. За циклом, в котором один из стробов данных устанавливается низким, следует цикл, в котором один или оба строба устанавливаются низкими.......................69

2.25 Временная диаграмма пересытки данных. ЗАДАТЧИК, ИСПОЛНИТЕЛЬ и ШИННЫЙ ТАЙМЕР. (Цикл с тайм-аутом) ...................70

VI

ГОСТ Р МЭК 821-2000

2.26 Временная диаграмма передачи управления тиной пересылки данных. ЗАДАТЧИ К ... 71

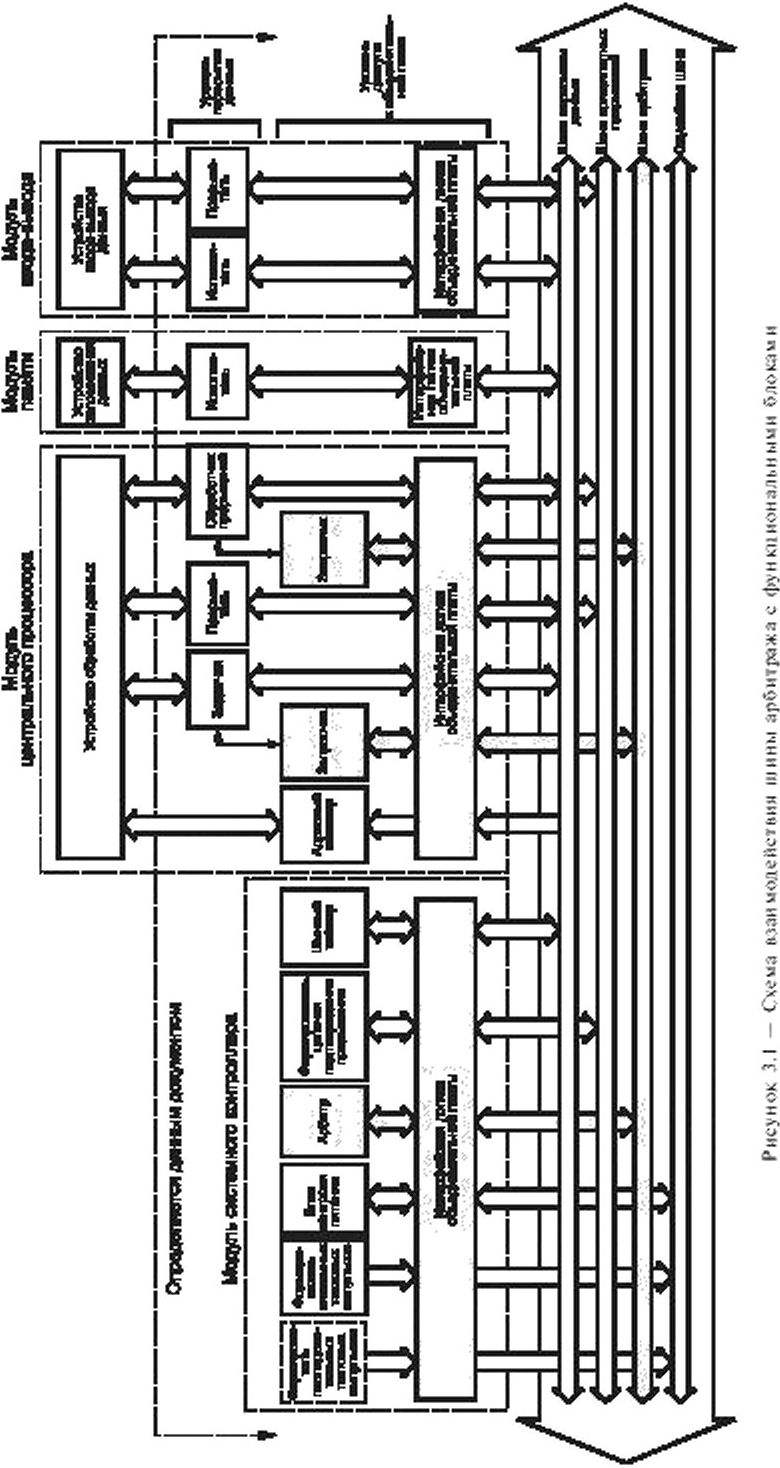

3.1 Схема взаимодействия шины арбитража с функциональными блоками......73

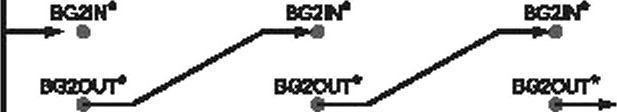

3.2 Иллюстрация последовательных цепочек предоставления шины.........74

3.3 Схема взаимодействия арбитра с магистралью VME............76

3.4 Схема взаимодействия запросчика с магистралью VME............77

3.5 Алгоритм арбитража. Два запросчика, два уровня запросов...........82

3.6 Диаграмма последовательности арбитража. Два запросчика, два уровня запросов .... 85

3.7 Алгоритм арбитража. Два запросчика, один и тот же уровень запроса.......86

3.8 Диаграмма последовательности арбитража. Два запросчика, один и тот же уровень запросов 90

4.1 Схема взаимодействия шины приоритетных прерываний с функциональными блоками . . 92

4.2 Структурная схема системы прерывания с одним обработчиком........93

4.3 Структурная схема распределенной системы прерывания...........94

4.4 Последовательная цепочка IACKIN*/1ACKOUT*............95

4.5 Схема взаимодействия обработчика прерываний с магистралью VME.......96

4.6 Схема взаимодействия прерывателя с магистралью VME...........98

4.7 Схема взаимодействия формирователя цепочки подтверждения прерывания с магистралью VME..........................99

4.8 Освобождение линий запроса прерывания прерывателями типов ROAK и RORA . . . 102

4.9 Формирователь цепочки подтверждения прерывания и прерыватель в одном и том же модуле 103

4.10 Два прерывателя в одном и том же модуле...............104

4.11 Три фазы последовательности обработки прерывания............104

4.12 Два обработчика прерываний, каждый из которых контролирует одну линию запроса прерывания ..........................106

4.13 Два обработчика прерываний, каждый из которых контролирует несколько линий запроса прерывания........................106

4.14 Алгоритм работы системы прерывания с одним обработчиком..........107

4.15 .Алгоритм работы распределенной системы прерывания с двумя обработчиками прерываний 111

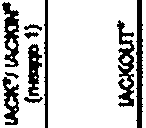

4.16 Временная диаграмма выбора прерывателя. ОБРАБОТЧИК ПРЕРЫВАНИЙ и ПРЕРЫВАТЕЛЬ. (Одно-, двух- и четырехбайтовые циклы подтверждения прерывания).....123

4.17 Временная диаграмма выбора прерывателя. ФОРМИРОВАТЕЛЬ ПЕНОЧКИ ПОДТВЕРЖ-

ДЕНИЯЯ ПРЕРЫВАЙ ИЯЯ. (Одно-.двух- и четырехбайтовые циклы подтверждения прерывания) ..........................124

4.18 Временная диаграмма выбора прерывателя. Участвующий ПРЕРЫВАТЕЛЬ. (Одно-, двух- и четырехбайтовые циклы подтверждения прерывания)............125

4.19 Временная диаграмма выбора прерывателя. Отвечающий ПРЕРЫВАТЕЛЬ. (Одно-, двух- и четырехбайтовые циклы подтверждения прерывания)............126

4.20 Временная диаграмма пересылки информации статуса/идентификации. ОБРАБОТЧИК ПРЕРЫВАНИЙ. (Однобайтовый никл подтверждения прерывания)........127

4.21 Временная диаграмма пересылки информации статуса/идентификации. ОБРАБОТЧИК ПРЕ

РЫВАНИЙ. (Двух- и четырехбайтовый циклы подтверждения прерывания) . . . .128

4.22 Временная диаграмма пересылки информации статуса/идентификации. Отвечающий ПРЕРЫВАТЕЛЬ. (Однобайтовый никл подтверждения прерывания).........129

4.23 Временная диаграмма пересылки информации статуса/идентификации.Отвечающий ПРЕРЫВАТЕЛЬ. (Двух- и четырехбайтовый циклы подтверждения прерывания).....130

4.24 Временная диаграмма работы цепочки подтверждения прерывания между циклами ФОР-

МИ РОВАТЕЛЬ ЦЕПОЧКИ ПОДТВЕРЖДЕНИЯЯ ПРЕРЫВАНИЯЯ, отвечающий ПРЕРЫ-ВАТЕЛ Ь и участвующий 11РЕРЫ ВАТЕЛ Ь................131

5.1 Схема взаимодействия служебной шины с функциональными блоками.......133

5.2 Временная диаграмма работы формирователя системного тактового сигнала......134

5.3 Схема взаимодействия блока контроля питания с устройствами магистрали VME . . . .134

5.4 Временная диаграмма работы блока контроля питания в случае отказа питания.....135

5.5 Временная диаграмма работы блока контроля питания при включении системы.....135

5.6 Временная диаграмма сигналов SYSRESET* и SYSFAIL*...........137

5.7 Опенка значения тока для контактов питания..............138

6.1 Уровни логических сигналов...................140

VII

ГОСТ Р МЭК 821-2000

6.2 Стандартные оконечные нагрузки магистрали..............145

6.3 11оперечное сечение микрополосковой сигнальной линии объединительной платы . . . 146

6.4 Зависимость волнового сопротивления.? от ширины сигнальной линии......146

6.5 Зависимость погонной емкости С„от ширины сигнальной линии........147

7.1 Каркас с модулями разной высоты.................156

7.2 Основные размеры печатной платы одинарной высоты............157

7.3 Основные размеры печатной платы двойной высоты.............158

7.4 Расположение соединителей на платах одинарной и двойной высоты........159

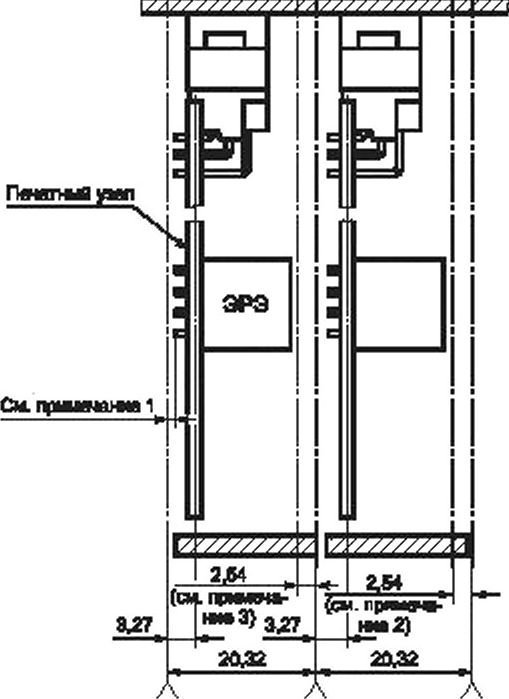

7.5 Поперечный разрез печатной платы, соединителя, объединительной платы и передней панели..........................160

7.6 Высота ЭРЭ, длина выводов, коробление печатных плат...........161

7.7 Передняя панель одинарной высоты, одинарной ширины...........162

7.8 Передняя панель двойной высоты, одинарной ширины............163

7.9 Крепежные угольники передней панели и размеры модуля одинарной высоты.....164

7.10 Крепежные угольники передней панели и размеры модуля двойной высоты.....165

7.11 Панель-заглушка одинарной высоты.................166

7.12 Панель-заглушка двойной высоты.................167

7.13 Габаритные и присоединительные размеры объединительных плат Л и J2.....168

7.14 Детальные размеры объединительных плат Л и J2............169

7.15 Габаритные и присоединительные размеры комбинированной объединительной платы J1/J2 170

7.16 Детальные размеры комбинированной объединительной платы JI/J2.......171

7.17 Расположение оконечных нагрузок вне объединительной платы (вил на объединительную плату сверху).......................172

7.18 Расположение оконечных нагрузок непосредственно на объединительной плате (вид на объединительную плату сверху) ....................173

7.19 Каркас на 21 гнездо......................173

7.20 Направляющие модулей.....................174

Перечень таблиц

2.1 Категории байтовых ячеек....................12

2.2 Использование сигналов DS0*, DS1*, Л01 и LWORD* для выбора байтовых ячеек ... 12

2.3 Колы модификатора адреса....................14

2.4 Использование линий данных для доступа к байтовым ячейкам.........16

2.5 Задатчики. Правила и разрешения для контроля и возбуждения сигнальных линий, отмеченных на рисунке 2.2 пунктиром ...................18

2.6 Исполнители. Правила и разрешения для контроля и возбуждения сигнальных линий, отмеченных на рисунке 2.3 пунктиром..................19

2.7 Использование мнемонического обозначения ВТО(х) для указания тайм-аута шинных тай-меров.........................20

2.8 Адресный монитор. Правила и разрешения для контроля сигнальных линий, отмеченных на рисунке 2.5 пунктиром....................21

2.9 Мнемонические обозначения режимов адресации..............22

2.10 Мнемонические обозначения основных возможностей пересылки данных......24

2.11 Мнемоническое обозначение возможностей блочных пересылок.........26

2.12 Мнемоническое обозначение возможностей цикла Чтение— Модификация—Запись .... 27

2.13 Пересылка 32 разрядов данных с использованием кратнобайтовых циклов......28

2.14 Пересылка 16 разрядов данных с использованием кратнобайтовых циклов......29

2.15 Мнемоническое обозначение возможности невыровненных пересылок......30

2.16 Мнемоническое обозначение возможности цикла Только Адрес.........30

2.17 Перечень временных диаграмм, определяющих работу задатчиков, отвечающих исполнителей и адресных мониторов (временные параметры указаны в таблице 2.22)......39

2.18 Определение мнемонических обозначений, употребляемых в таблицах 2.19—2.21 .... 40

VIII

ГОСТ РМЭК 821-2000

2.19 Использование адресных линий для выбора четырехбайтовой группы.......41

2.20 Использование DSO*. DSI*, Л01 и LWORD* во время различных циклов......42

2.21 Использование линий данных для пересылки данных............43

2.22 Значения параметров временных соотношений для задатчика, исполнителя и адресного монитора ..........................45

2.23 Значения параметров временнйх соотношений для шинного таймера........46

2.24 Задатчик. Правила и замечания по временном соотношениям.........46

2.25 Исполнитель. Правила и замечания по временном соотношениям........49

2.26 Адресный монитор. 'Замечания по временном соотношениям..........52

2.27 Шинный таймер. Правила по временном соотношениям..........53

3.1 Арбитры. Правила и разрешения для возбуждения и контроля сигнальных линий, отмеченных на рисунке 3.3 пунктиром....................77

3.2 Запросчики. Правила и разрешения для возбуждения и контроля сигнальных линий, отмеченных на рисунке 3.4 пунктиром.................78

4.1 Обработчик прерываний. Правила и разрешения для возбуждения и контроля сигнальных линий, отмеченных на рисунке 4.5 пунктиром..............96

4.2 11рерыватели. I (равила и разрешения для возбуждения и контроля сигнальных линий, отмеченных на рисунке 4.6 пунктиром.................99

4.3 Использование мнемонического обозначения 1Н( )для описания возможностей обработки прерываний........................100

4.4 Использование мнемонического обозначения 1() для описания возможностей формирования запроса прерывания......................100

4.5 Мнемонические обозначения для описания возможностей по пересылке информации стату-са/идеитификаиии.......................100

4.6 Мнемонические обозначения для описания возможностей освобождения линии запроса прерывания ..........................102

4.7 Трехразрядный кол подтверждения прерывания..............НО

4.8 Перечень временнйх диаграмм, определяющих работу обработчика прерываний и прерывателя ..........................113

4.9 Перечень временнйх диаграмм, определяющих работу формирователя цепочки подтверждения прерывания .......................114

4.10 Перечень временнйх диаграмм, определяющих работу участвующего прерывателя . . .114

4.11 Перечень временнйх диаграмм, определяющих работу отвечающего прерывателя . . .114

4.12 Определение мнемонических обозначений, используемых в таблицах 4.13—4.15 . . . .114

4.13 Использование линий AOI— ЛОЗ и 1АСК* во время циклов подтверждения прерывания . .115

4.14 Использование линий DSP. DSO4. LWORD* и WRITE* во время циклов подтверждения прерывания........................115

4.15 Использование линий данных D00—D31 для пересылки информации статуса/илеитифика-ЦИН..........................116

4.16 Значения параметров временнйх соотношений для обработчиков прерываний, прерывателей и формирователей цепочки подтверждения прерывания...........116

4.17 Обработчик прерываний. Правила и замечания по временнйм соотношениям.....117

4.18 Прерыватель. Правила и замечания по временнйм соотношениям........119

4.19 Формирователь цепочки подтверждения прерывания. Правила и замечания по временнйм соотношениям.......................122

5.1 Правила возбуждения функциональными блоками сигналов в процессе включения и выключения питания.......................136

6.1 Технические характеристики питающих напряжений магистрали.........139

6.2 Требования к характеристикам формирователей и приемников сигналов магистрали . .141

6.3 Сводная таблица типов формирователей магистрали............148

7.1 Распределение сигналов по контактам соединителей Л/Р 1..........175

7.2 Распределение сигналов по контактам соединителей J2/P2..........176

1.2’ IX

ГОСТ Р МЭК 821-2000

Введение

Настоящий стандарт определяет магистраль, реализуемую на объединительной плате (объединительных платах) и обладающую высокими техническими характеристиками. Магистраль предназначена ятя использования в микрокомпьютерных системах, в которых задействованы один или несколько микропроцессоров.

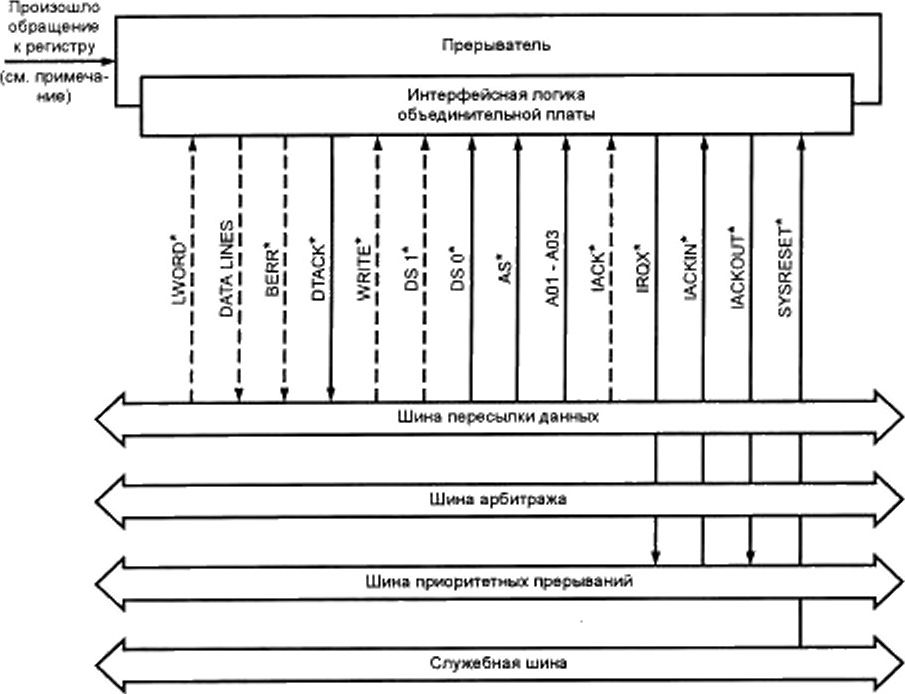

Основой стандарта являются «-Общие технические требования на магистраль \ М Е». изданные группой изготовителей VME-магистральных изделий в августе 19X2 г. Магистраль VME состоит из следующих четырех субмагистралей (далее — шин): шины пересылки данных, шипы приоритетных прерываний, шины арбитража и служебной шины.

Шина пересылки данных выполняет Х-. 16- и 32-разрядные пересылки данных. Линии данных и адресов не мультиплексируются. Протоколы пересылки являются асинхронными. Пересылки полностью квитируются. Шина приоритетных прерываний обеспечивает прерывания в реальном времени. Передача управления магистралью выполняется шиной арбитража, которая позволяет реализовать алгоритмы кругового и приоритетного арбитража. Служебная шина обеспечивает синхронизацию в процессе включения и выключения питания. Требования к механическим конструкциям модулей, объединительных плат, каркасов и оболочек основаны на соответствующих требованиях Публикации МЭК 111.12|.

Перечень нормативной документации, на которую делаются ссылки в настоящем стандарте, приведен в ссылочных материалах.

Настоящий стандарт соответствует международному стандарту' МЭК Х21 (второе издание. 1991 г.).

X

ГОСТ Р МЭК 821-2000

ГОСУДАРСТВЕННЫЙ СТАНДАРТ РОССИЙСКОЙ ФЕДЕРАЦИИ

МАГИСТРАЛЬ МИКРОПРОЦЕССОРНЫХ СИСТЕМ ДИЯЯ ОБМЕНА ИНФОРМАЦИЕЙ РАЗРЯЯДНОСТЬЮ ОТ 1 ДО 4 БАЙТОВ (МАГИСТРАЛЬ УМЕ)

I ЕС 821 VME bus.

Microprocessor system bus lor 1 byte to 4 byte data

Дата введения 2001—01—01

1 Область применения

1.1 Назначение стандарта магистрали УМЕ

Настоящий стандарт устанавливает требования к интерфейсной системе, используемой для взаимного соединения устройств обработки, запоминания данных и управления периферией (в дальнейшем — устройств) в единый аппаратный комплекс, и предназначен для решения следующих задач:

- обеспечение обмена информацией между устройствами по магистрали без вмешательства во внутренние операции других устройств, сопряженных с этой магистралью;

- определение электрических и конструктивных характеристик системы, необходимых для проектирования устройств, которые будут иметь надежную и однозначную связь с другими устройствами. сопряженными с магистралью;

- установление протоколов, которые однозначно определяют порядок взаимодействия между магистралью и сопряженными с ней устройствами;

- введение терминов и определений, которые употребляются для описания системного протокола;

- предоставление существенной свободы проектирования, позволяющей разработчику оптимизировать стоимость и/или рабочие характеристики, не влияющие на системную совместимость;

- предоставление системы, в которой рабочие характеристики в основном ограничиваются устройствами, а не интерфейсной системой.

1.2 Элементы интерфейсной системы

1.2.1 Основные определения

Структура магистрали VME может быть описана с двух точек зрения: механической конструкции и функциональной структуры.

Конструктивные технические требования содержат данные о физических размерах каркасов, объединительных плат, передних панелей, модулей и т.д.

Функциональные технические требования содержат данные о принципах работы магистрали, функциональных блоков, задействованных в каждой операции, и правилах, которые определяют их поведение.

Данный раздел содержит не претендующие на строгость определения некоторых основных терминов, употребляемых для описания структурной схемы и механических конструкций магистрали VME

1.2.1.1 Термины, используемые для описания механических конструкций магистрали УМЕ объединительная плата (backplane): Печатная плата с 96-контактными соединителями и печатными сигнальными проводниками, которые соединяют соответствующие контакты этих соединителей. Некоторые системы магистрали VME имеют единственную печатную плату объединительную

Издание официальное

I »- IM4

1

ГОСТ Р МЭК 821-2000

плату Л. Она содержит печатные сигнальные проводники, требуемые для выполнения основных операций. Другие системы магистрали VM Е имеют также дополнительную печатную плату — объединительную плату J2. Она содержит дополнительные 96-контактные соединители и печатные сигнальные проводники, требуемые для пересылок данных и адресов повышенной разрядности. Наконец, третьи имеют комбинированную печатную плату — объединительную плату JI/J2. которая содержит печатные сигнальные проводники и соединители объединительных плат JI и J2.

модуль (board): Печатная плата с набором электрорадиоэлементов и одним или двумя 96-кон-тактными соединителями, которые могут сочленяться с соединителями объединительной платы.

гнездо (slot): Место перед объединительной платой (платами), куда помешается модуль для сочленения с соединителем (соединителями) этой платы. Если система имеет обе платы Л и J2 или комбинированную объединительную плату JI/J2, то каждое гнездо имеет два 96-контактных соединителя. Если система имеет только одну плату Л, то каждое гнездо имеет один 96-контактный соединитель.

каркас (subrack): Жесткая рамочная иссушая конструкция, обеспечивающая механическую поддержку модулей, вставляемых в объединительную плату, надлежащее сочленение соединителей, отсутствие контакта между соседними модулями, распределение охлаждающих воздушных потоков в системе и невозможность нарушения контакта между вставленными модулями и объединительной платой вследствие вибрации или ударов.

1.2.1.2 Термины, используемые для описания функциональной структуры магистрали УМЕ

На рисунке 1.1 приведена упрощенная схема функциональной структуры системы, содержащая сигнальные линии, интерфейсную логику объединительной платы и функциональные блоки.

Модуль цент раланого процасрора

Модуль паияти

Модула пмда-тялди

2

УсТМЙСТИ s€p©f< m ДЛИ!»».

Устройство iiiwiwwmu ^31На>

Устолктос «|рда смода данных

Рулкцис-игмые блог

НАПаНЫЙ блок.

ФуНКДО-илль-ый блок

Интесфейсная лоъкг обьвдииителы-а* спета

ИМГ0РФ41ЧММ логи га

О 5ь ОД И и ИТОГ»: но Д

Сингли» линии ^мпммАтм

Интерфейс сметами.

определяема» iucicim'» си-дарг:*

Ф>мкцро-ииьный блок

Функциональный блок

ИиторфОЙСНМ ЛОШЙ объединительной rwbl

Рисунок 1.1 — Элементы системы, определенные настоящим стандартом

ГОСТ Р МЭК 821-2000

интерфейсная логика объединительной платы магистрали VME (backplane interface logic): Определенная логика, учитывающая характеристики объединительной платы: полное сопротивление ее сигнальных линий, время распространения сигналов, значения оконечных нагрузок и т. д. Настоящий стандарт устанавливает правила проектирования такой логики с учетом максимальной длины объединительной платы и максимального количества гнезд для модулей.

функциональный блок (functional module): Совокупность электронных схем, расположенных на одном модуле магистрали VME и совместно выполняющих какую-то определенную задачу.

шина пересылки данных (data tansfer bus): Одна из четырех шин объединительной платы. Позволяет задатчикам устанавливать направление пересылок двоичных данных между ними и исполнителями.

цикл шины пересылки данных (data transfer bus cycle): 11оследователыюсть перепадов напряжения логических уровней на сигнальных линиях шины пересылки данных, которая реализует пересылку адреса или адреса и данных между задатчиком и исполнителем. Цикл шины пересылки данных подразделяется на две части:

- широковещательная пересылка адреса:

- пересылка данных, если она предусмотрена.

Предусмотрено 34 типа циклов шины пересылки данных. Они определены ниже в данном разделе.

задатчик (master): Функциональный блок, который инициирует циклы шины пересылки данных для пересыпки данных между ним и исполнителем.

исполнитель (slave): Функциональный блок, который обнаруживает циклы шины пересылки данных, инициируемые задатчиком, и. когда эти циклы предусматривают его (исполнителя) участие. осуществляет пересылки данных между собой и задатчиком.

адресный монитор (location monitor): Функциональный блок, контролирующий пересылки по шине пересылки данных с целью обнаружения обращений к ячейкам, которые ему подписано контролировать. Если происходит обращение к одной из этих ячеек, адресный монитор вырабатывает внутримодульный сигнал.

шинный таймер (bus timer): Функциональный блок, который выполняет отсчет времени каждой пересылки по шине пересыпки данных и завершает никл шины, если это время превышает разумные пределы. Без этого блока может возникнуть ситуация, при которой задатчик попытается выполнить операцию пересылки данных в/из какой-то несуществующей ячейки исполнителя и неопределенно долго ждать результаты. Шинный таймер предотвратит эту задержку завершением цикла.

шина приоритетных прерываний (priority interrupt bus): Одна из четырех шин объединительной платы магистрали VME, которая позволяет прерывателям посылать запросы прерывания обработчикам прерываний.

прерыватель (interrupter): Функциональный блок, формирующий запрос прерывания на шине приоритетных прерываний, а затем предоставляющий информацию статуса/идентификации по требованию обработчика прерываний.

обработчик прерываний (interrupt handler): Функциональный блок, обнаруживающий запросы прерывания, которые формируются прерывателями, и отвечающий на эти запросы требованием о предоставлении ему информации статуса/идентификации.

последовательная цепочка (далее — цепочка) (daisy—chain): Определенный тип сигнальной линии магистрали VME, используемой для распространения уровня сигнала от модуля к модулю, начиная с первого гнезда и кончая последним гнездом. Магистраль VME имеет четыре цепочки предоставления шины и одну цепочку подтверждения прерывания.

формирователь последовательной цепочки подтверждения прерывания (LACK (interrupt acknowledge) daisy-chain driver): Функциональный блок, устанавливающий в активное состояние цепочку подтверждения прерывания всякий раз, когда обработчик прерываний подтверждает запрос прерывания. Такая цепочка гарантирует пересылку информации о статусе/идентификации по шине пересылки данных только от одного прерывателя, лаже если запрос прерывания сформирован несколькими прерывателями.

шина арбитража (arbitration bus): Одна из четырех шин объединительной платы магистрали VME. Позволяет одному арбитру и нескольким запросчикам координировать порядок использования шины пересылки данных.

запросчик (requester): Функциональный блок, находящийся на одной плате с задатчиком или обработчиком прерываний и запрашивающий право на использование шины пересылки данных всякий раз, когда это потребуется его задатчику или обработчику прерываний.

i.r 3

ГОСТ Р МЭК 821-2000

арбитр (arbiter): Функциональный блок, который принимает запросы на использование шины от запросчиков и предоставляет управление шиной пересылки данных одновременно только одному запросчик.

служебная шина (utility bus): Одна из четырех шин объединительной платы магистрали VME. по которой перелаются периодические системные синхросигналы и сигналы, координирующие последовательность действий системы при включении и выключении питания.

формирователь системного тактового сигнала (system clock driver): Функциональный блок, подающий на служебную шину синхронизирующий сигнал частотой 16 М Гц.

формирователь тактового сигнала последовательной магистрали (serial clock driver): Функциональный блок, подающий периодический тактовый сигнал, который синхронизирует работу магистрали МЭК 823 |5|. Хотя стандарт магистрали VME определяет формирователь тактового сигнала последовательной пересылки и в нем предусматриваются две сигнальные линии на объединительной плате, используемые магистралью МЭК 823. протокол последней абсолютно не зависит от магистрали VME.

Технические требования к временным параметрам для формирователя тактового сигнала последовательной магистрали приведены в приложении С.

блок контроля питания (power monitor module): Функциональный блок, контролирующий состояние первичного источника питания системы магистрали VME и сигнализирующий о выходе параметров питания за пределы, гарантирующие надежную работу системы. Поскольку большинство систем запитываются от источника переменного тока, блок контроля питания обычно проектируется с возможностью обнаружения состояния обесточивания сети переменного тока.

модуль системного контроллера (system controller board): Модуль, размещаемый в гнезде 1 объе-линительной платы магистрали VME и имеющий в своем составе формирователь системного тактового сигнала, арбитр, формирователь цепочки подтверждения прерывания и шинный таймер. Некоторые контроллеры содержат также формирователь тактового сигнала последовательной пересылки либо блок контроля питания, либо то и другое.

1.2.1.3 Типы циклов магистрали УМЕ

цикл считывания (read cycle): Цикл шины пересылки данных, используемый для пересылки одного, двух, трех или четырех байтов от исполнителя задатчику. Цикл начинается, когда задатчик выполняет широковещательную пересылку адреса и модификатора адреса. Каждый исполнитель принимает адрес и модификатор адреса и проверяет, не он ли должен отвечать в этом цикле считывания. Если это так. он извлекает данные из своей внутренней памяти, помешает их на шину пересылки данных и подтверждает пересылку. После этого задатчик завершает никл.

цикл записи (write cycle): Цикл шины пересылки данных, используемый для пересылки одного, двух, трех или четырех байтов от задатчика исполнителю. Цикл начинается, когда задатчик выполняет широковещательную пересылку адреса и модификатора адреса и помешает данные на шину пересылки данных. Каждый исполнитель принимает адрес и модификатор адреса и проверяет, не он ли должен отвечать в этом цикле. Если это так. он запоминает эти данные и затем подтверждает пересылку. 11осле этого задатчик завершает цикл.

цикл блочного считывания (block read cycle): Никл шины пересылки данных, используемый для пересылки блока размером от I до 256 байтов от исполнителя задатчику. Эта пересылка выполняется с использованием ряда последовательных одно-, двух- или четырехбайтовых пересылок. После начата блочной пересылки задатчик не освобождает шину пересылки данных до тех пор. пока им не будут считаны все байты. Цикл блочного считывания отличается отряда из нескольких обычных циклов считывания тем. что задатчик только один раз (в начале цикла) выполняет широковещательную пересылку адреса и модификатора адреса. Затем при каждой пересылке исполнитель наращивает этот адрес, чтобы данные для следующей пересылки извлекались из следующей ячейки.

цикл блочной записи (block write cycle): Цикл шины пересылки данных, используемый для пересылки блока размером от I до 256 байтов от задатчика исполнителю. Эта пересылка выполняется с использованием ряда последовательных одно-, двух- или четырехбайтовых пересылок данных. Задатчик не освобождает шину пересылки данных до тех пор. пока не будут переданы все байты. Никл блочной записи отличается отряда из нескольких обычных циклов записи тем. что задатчик только один раз (в начале никла) выполняет широковещательную пересылку адреса и модификатора адреса. Затем исполнитель наращивает этот адрес при каждой пересылке, чтобы данные следующей пересылки записывались в следующую ячейку.

4

ГОСТ Р МЭК 821-2000

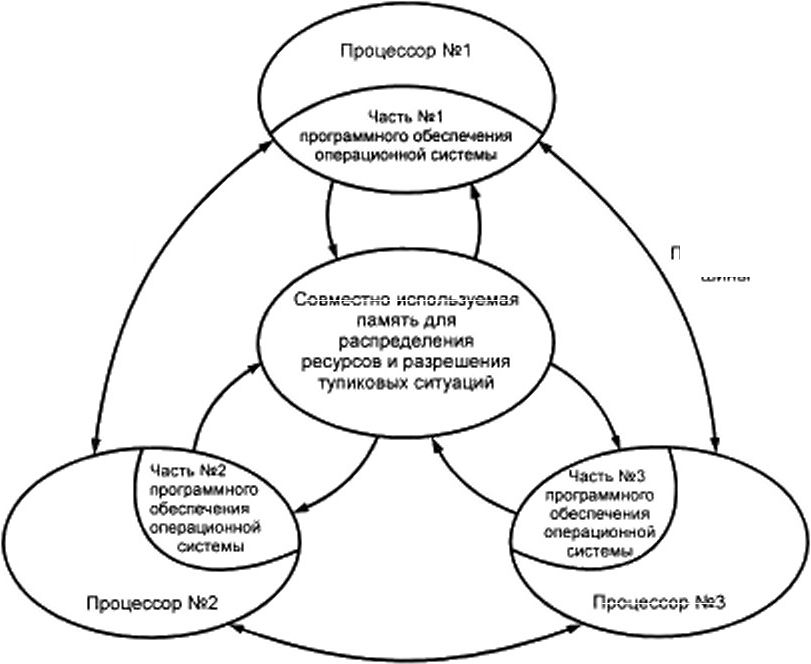

цикл Чтение—Модификация—Запись (read—modify—write cycle): Цикл шины пересылки данных, используемый задатчиком для обращения к ячейке исполнителя как п режиме считывания, так и в режиме записи при запрещении доступа к этой ячейке со стороны других задатчиков. Этот цикл очень полезен для мультипроцессорных систем, в которых определенные ячейки памяти используются для выполнения семафорных функций.

цикл Только Адрес (address—only cycle): Цикл шины пересылки данных, состоящий только из широковещательной пересылки адреса без пересылки данных. Исполнители не подтверждают такие никлы, а задатчики завершают такой никл, не ожидая подтверждения.

цикл подтверждения прерывания (interrupt acknowledge cycle): Цикл шины пересылки данных, инициируемый обработчиком прерываний, который выполняет считывание информации статуса/ идентификации от прерывателя. Обработчик прерываний вырабатывает этот никл всякий раз, когда обнаруживает запрос прерывания от прерывателя, а шина пересылки данных находится под его управлением.

1.2.2 Основная структура магистрали VME

Интерфейсная система магистрали VME состоит из интерфейсной логики объединительной платы, четырех групп сигнальных линий, называемых шинами, и набора функциональных блоков, которые могут быть сконфигурированы так. как это необходимо. Функциональные блоки взаимодействуют между собой, используя сигнальные линии объединительной платы.

Функциональные блоки, определенные настоящим стандартом, служат средством описания протокола магистрали и их не следует рассматривать как ограничение при проектировании интерфейсной логики. Например, разработчик может спроектировать логику, взаимодействующую с магистралью VME описанным способом, но использующую другие внутримодульные сигналы или контролирующую дополнительно другие сигналы магистрали VME. Модули магистрали VME можно проектировать из различных комбинаций функциональных блоков, определенных настоящим стандартом.

Функциональная структура магистрали VME подразделяется на четыре категории. Каждая состоит из шины и подсоединенных к ней функциональных блоков, выполняющих совместно свои конкретные задачи. Функциональные блоки и шины магистрали изображены на рисунке 1.2. Каждая категория функциональной структуры кратко описана ниже.

Шина пересылки данных. Устройства пересылают данные по шине пересылки данных, состоящей из магистральных линий данных, адреса и соответствующих управляющих сигналов. Функциональные блоки (задатчики, исполнители, прерыватели и обрабогшки прерываний) используют шину пересылки данных для обмена данными между собой. В этом процессе им оказывают содействие два других блока: шинный таймер и формирователь последовательной цепочки подтверждения прерывания.

Шина арбитража. Поскольку системы магистрали могут конфигурироваться с несколькими задатчиками или обработчиками прерываний, предусмотрен механизм, который упорядоченным способом выполняет передачу управления шиной пересылки данных от одного блока к другому и гарантирует соблюдение правила: в любой заданный момент времени только один из них управляет шиной пересылки данных. Передачу управления координируют функциональные блоки шины арбитража (запросчики и арбитр).

Шина приоритетных прерываний. Функциональная возможность приоритетных прерываний магистрали VME является средством, с помощью которого устройства могут запрашивать обслуживание от обработчиков прерываний. Эти запросы порываний могут быть подразделены по приоритету максимально на семь уровней. Прерыватели и обработчики прерываний используют сигнальные линии шины приоритетных прерываний.

Служебная шина. Служебная шина обеспечивает следующие функции: передачу периодических тактовых сигналов, выполнение операций инициализации и обнаружение отказов. Шина состоит из двух линий тактовых сигналов, линии сигнала системного сброса, линии сигнала системного отказа, линии сигнала отказа сети переменного тока и линии данных последовательной магистрали пересылки.

1.3 Диаграммы, используемые в стандарте магистрали VME

Для более наглядного описания протоколов магистрали VME используются три типа диаграмм, перечисленных ниже.

Временное диаграммы. Изображают временное соотношения между изменениями сигналов. Указанные временное параметры имеют минимальные и/или максимальные значения. Некоторые времен -

5

ГОСТ Р МЭК 821-2000

6

ГОСТ РМЭК 821-2000

nfle параметры определяют поведение интерфейсной логики объединительной платы, другие - поведение функциональных блоков в их взаимосвязи.

Диаграммы последовательностей. Аналогичны временной диаграмме, но показывают лишь временные соотношения взаимосвязи функциональных блоков. Они показывают последовательность событий, но не определяют соответствующие им временное параметры. Например, диаграмма последовательности может показать, что блок Л не сможет сформировать изменение состояния сигнала В до тех пор, пока он не обнаружит, что блок С изменил состояние сигнала D.

Схемы последовательностей. Показывают порядок следования событий, по мере того как они происходят во время работы магистрали VM Е. События формулируются словами и являются результатом взаимодействия двух или более функциональных блоков. Схемы последовательностей дают описание операций магистрали в последовательном порядке и одновременно показывают, как именно взаимодействуют функциональные блоки.

1.4 Терминология

Чтобы избежать путаницы и четко определить требования, нуждающиеся в согласованности, многие абзацы настоящего стандарта озаглавлены ключевыми словами, которые указывают на тип содержащейся в них информации. Это следующие слова:

- Привило

- Рекомендация

- Предложение

- Разрешение

- Замечание

В тексте за ключевым словом следуют числа, разделенные точкой и обозначающие: первое — номер раздела стандарта, второе — индивидуальный номер данного типа информации в разделе.

Любой текст, не имеющий в качестве заголовка перечисленных ключевых слов, является описательной частью структуры интерфейсной системы или ее работы. Он имеет описательную или повествовательную форму. Ниже приводятся указания по использованию ключевых слов.

Привило. Правила образуют основу данного стандарта и .могут быть представлены в виде текстов, рисунков, таблиц или чертежей. Все правда ДОЛЖНЫ СОБЛЮЛА ТЬСЯ неукоснительно с целью обеспечении совместимости изделии магистрали УМЕ. Правила характеризуются употреблением императивных оборотов с использованием модального глагола долженствования (ДОЛЖЕН, НЕ ДОЛЖЕН) и смыслового глагола в неопределенной форме, выделяемых в тексте прописными буквами и употребляемых в зтом виде исключительно для формулирования правил.

Рекомендация. Разработчику следует выполнять все рекомендации, содержащиеся в стандарте. Игнорирование рекомендаций может привести к возникновению тупиковых ситуаций или ухудшению характеристик системы. Магистраль VME разработана для реализации высокопроизводительных систем, но можно спроектировать систему, формально соответствующую всем правилам, но имеющую очень низкую производительность. Во многих случаях разработчику нужно обладать определенным опытом проектирования модулей, которые обеспечивали бы наивысшую производительность. Рекомендации основываются именно на таком опыте и дают разработчику соответствующую информацию для его освоения.

Предложение. Предложение содержит совет, который является полезным, но не имеет первостепенной важности. Прежде чем отвергнуть этот совет, разработчику предлагается его рассмотреть. Без приобретенного опыта некоторые решения при проектировании принимать очень сложно. Предложения имеют цель помочь разработчику в приобретении такого опыта. Некоторые предложения касаются проектирования модулей с возможностью их несложной переконфигурации для совместной работы с другим модулем или упрощения отладки системы и т.д.

Разрешение. В некоторых случаях правила не содержат специальных запретов по методам проектирования, однако разработчик может оказаться в затруднении, решая вопрос о правомерности применения этих методов и вероятности возникновения при этом каких-либо неожиданных проблем. Разрешение убеждает разработчика, что какой-то определенный подход является приемлемым и не вызовет никаких ошибок. Для формулирования разрешений употребляется модальный глагол МОЧЬ (МОЖЕТ. МОГУТ, МОЖНО), выделяемый в тексте разрешений прописными буквами. Глагол МОЧЬ в таком виде употребляется исключительно для этой цели.

Замечание. Замечания не содержат каких-то конкретных советов. Обычно они являются естественным продолжением только что рассмотренных вопросов. Они разъясняют смысл некоторых

ГОСТ Р МЭК 821-2000

правил и обращают внимание на те стороны, которые без этих разъяснений могут оказаться упущенными. Они содержат также обоснование введения определенных правил, чтобы разработчик понимал, по какой причине эти правота должны соблюдаться.

1.4.1 Состояния сигнальных линий

Настоящий стандарт устанавливает протоколы магистрали, описание которых дается в терминах логических уровней сигналов и их переходов с одного уровня на другой на линиях магистрали. Предполагается, что сигнал на любой линии всегда имеет один из двух уровней или находится в состоянии перехода между этими уровнями. При употреблении термина ВЫСОКИЙ подразумевается высокий уровень напряжения схем транзисторно-транзисторной логики (ТТЛ), термином НИЗКИЙ обозначается низкий уровень напряжения схем ТТЛ. Если напряжение изменяется между этими уровнями, то сигнал на линии находится в состоянии перехода (информация по пороговым напряжениям магистрали VME содержится в разделе 6).

На линии возможны два вида переходов сигнала, которые называются перепадами. Переход сигнала с низкого уровня на высокий называется положительным перепадом. Переход сигнала с высокого уровня на низкий называется отрицательным перепадом.

Техническими требованиями некоторых магистралей для этих перепадов устанавливаются максимальные или минимальные времена нарастания и спада сигнала. Однако проблема состоит в том. что разработчики модулей имеют мало возможностей контролировать эти времена. Если объединительная плата имеет большую нагрузку, времена нарастания и спада будут длительными. Если загрузка невелика, эти времена могут бьпь короткими. Даже если разработчики знают величины максимальной и минимальной нагрузок, все же потребуется время для лабораторных экспериментов, чтобы определить, какие формирователи сигналов обеспечат необходимые времена нарастания и спада. Эти времена являются результатом сложных взаимодействий ряда параметров, включающих волновое сопротивление сигнальной линии объединительной платы, величины ее оконечной нагрузки, внутреннее сопротивление источника формирователей и емкостную нагрузку сигнальной линии. Для выбора оптимального сочетания всех этих величин разработчику модулей необходимо изучить теорию линий передачи, а также некоторые специфические параметры формирователей и приемников, которые в документации большинства фирм-изготовителей обычно отсутствуют.

Учитывая изложенное, настоящий стандарт не устанавливает времена нарастания и спала. Вместо этого он определяет электрические характеристики формирователей и приемников и лает советы по проектированию объединительной платы. Он также информирует разработчиков, каким образом нагрузка магистрали для наихудшего случая повлияет на задержку распространения сигналов этих формирователей, чтобы еще до начата проектирования модуля они могли быть уверены в том, что требуемые временные соотношения будут соблюдены. Пользуясь этими рекомендациями, разработчики добьются надежной работы своего модуля при его взаимодействии с другими модулями магистрат VME для наихудших условий эксплуатации.

1.4.2 Использование звездочки (•)

В конце мнемонических обозначений сигналов при необходимости используется символ звездочки (♦). В этих случаях звездочка несет следующий смысл:

- звездочка в конце мнемонического обозначения сигнала, для которого имеет значение его уровень, показывает, что такой сигнал является истинным или достоверным, когда он установлен низким:

- звездочка в конце мнемонического обозначения сигнала, для которого имеет значение его перепад, показывает, что действия, инициируемые таким сигналом, происходят при его переходе с высокого на низкий логический уровень.

Замечание 1.1. Звездочка не применяется для асинхронно работающих сигналов SYSCLK (system clock) и SERCLK (serial clock). Между сигналами на этих линиях и другими сигналами магистрали фиксированных фазовых соотношений не устанавливается.

1.5 Технические требования к протоколу

Протокол магистрали имеет два уровня. Нижний уровень, называемый уровнем доступа к объединительной плате, состоит из интерфейсной логики объединительной платы, функциональных блоков служебной шины и функциональных блоков шины арбитража. Второй уровень, называемый уровнем пересылки данных, состоит из функциональных блоков шины пересылки данных и функциональных блоков шины приоритетных прерываний. Подразделение на уровни показано на рисунке 1.2.

Я

ГОСТ Р МЭК 821-2000

Замечание 1.2. Сигнальные линии, используемые функциональными блоками уровня пересылки данных, образуют особый класс, поскольку они возбуждаются в разные моменты времени разными функциональными блоками. Эти линии возбуждаются формирователями, которые в каждом функциональном блоке могут включаться и выключаться в зависимости от сигналов, формируемых на уровне доступа к объединительной плате. Очень важен строгий контроль за моментами времени включения и выключения формирователей, чтобы два формирователя не могли одновременно попытаться установить на одной и той же сигнальной линии два различных логических уровня. При определении момегиов времени их включения и выключения используется специальная система обозначений в виде временных диаграмм (см. рисунок 1.3).

Ликин НВ ■пвумдввтся

Линт нф ■ааЦмампя *н ИНЛ^ИД—НИ, носжтел на ЛИНИИ ш стабилен

Линия нмфждеетз» иснгнал Еттабилин

1Ъння НФ ■явуждавт^

Ж»

В магистрали используются два основных вила протоколов:

- протоколы замкнутого никла:

- протоколы открытого цикла.

Протоколы замкнутого пикта используют взаимосвязанные сигналы магистрали, а протоколы открытого цикла - широковещательные сигналы магистрали.

1.5.1 Взаимосвязанные сигналы магистрали

Взаимосвязанный сигнал магистрали посылается одним конкретным функциональным блоком в другой конкретный функциональный блок. Принимающий функциональный блок подтверждает получение сигнала. Взаимосвязь между двумя функциональными блоками длится до тех пор. пока сигнал не будет подтвержден.

Например, прерыватель может послать запрос прерывания, на который позже поступает ответ в виде сигнала подтверждения прерывания. Никаких временных ограничений при этом не устанавливается. Прерыватель не снимает запрос до тех пор. пока обработчик прерываний не подтвердит его.

9

ГОСТ Р МЭК 821-2000

Взаимосвязанные сигналы магистрали координируют исполнение внутренних функций системы и прог и во положи ость взаимодействию системы с внешними стимулирующими сигналами. Каждый взаимосвязанный сигнал имеет в рамках системы функциональный блок источника и функциональный блок назначения.

Особо важными взаимосвязанными сигналами являются строб адреса и стробы данных. Они взаимосвязаны с сигналами подтверждения пересылки данных и ошибки шины и координируют пересылку адресов и данных, которые являются основой всего информационного потока между функциональными блоками на уровне пересылки данных.

1.5.2 Широковещательные сигналы магистрали

Функциональный блок формирует широковещательный сигнал в ответ на какое-то событие. Протокол для подтверждения широковещательного сигнала не определен. Вместо этого предусмотрен механизм, обеспечивающий широковещательную передачу сигнала в течение минимально заданного времени, которое достаточно для его обнаружения всеми соответствующими функциональными блоками. Широковещательные сигналы могут быть сформированы в любой момент времени, независимо от любых других операций, выполняемых магистралью. Каждый из них посылается по своей специальной сигнальной линии. Примерами могут служить линии сигналов системного сброса и отказа сети питания переменного тока. Сигналы по этим линиям посылаются не какому-то конкретному функциональному блоку, а сообщают о возникновении особых условий всем функцио-нальным блокам.

1.6 Примеры функционирования систем и пояснения

Технические требования на протокол магистрали содержат подробное описание поведения различных функциональных блоков. В них рассмотрено, каким способом любой функциональный блок отвечает на какой-то сигнал без указания на происхождение сигнала. Из-за такой процедуры описания технические требования на протокол не дают полной картины. Чтобы помочь пользователю разоб-раться, настоящий стандарт содержит примеры типовых операций магистрали. В каждом таком примере приведена возможная последовательность событий, хотя возможны и другие последовательности. Существует опасность, что одновариантность последовательности событии в приведенных примерах будет восприниматься как единственно законный порядок операций, выполняемых магистралью. Во избежание такого неправильного восприятия все примеры приведены в повествовательной форме. Такое изложение противопоставлено строгому императивному стилю формулирования правил, обязательных для соблюдения соответствия настоящему стандарту.

2 Шина пересылки данных магистрали УМЕ

2.1 Введение

Магистраль УМЕ включает в себя высокоскоростную асинхронную параллельную шину пересылки данных. На рисунке 2.1 показана типичная система магистрали УМЕ. содержащая все функциональные блоки шины пересылки данных. Они выделены жирными линиями.

Задатчики используют шину пересылки данных для выбора ячеек памяти исполнителей, а также для пересылки данных в эти ячейки или из них. Некоторые задатчики и исполнители используют все линии шины пересылки данных, другие — только какое-то их подмножество.

Адресные мониторы отслеживают пересылку данных между задатчиком и исполнителями и вырабатывают внутримодульный сигнал всякий раз. когда осуществляется обращение к одной из байтовых ячеек, которую он контролирует. Например, он может просигнализировать своему внутри модул ь-ному процессору посредством запроса прерывания. В такой конфигурации, где процессорный модуль А производит запись в ячейку глобальной памяти магистрали УМЕ, контролируемую адресных! монитором процессора В. работа процессора В будет прервана.

После того, как задатчик инициирует цикл пересылки данных, он не завершит этот цикл до тех пор, пока не дождется ответа от отвечающего исполнителя. Асинхронный характер магистрали позволяет исполнителю тратить на ответ столько времени, сколько потребуется. Если исполнитель не в состоянии дать ответа из-за какой-то неисправности или при случайном обращении задатчика к ячейке, где нет исполнителя, вмешивается шинный таймер, позволяя циклу завершиться.

10

ГОСТ Р МЭК 821-2000

HReXOVQ НП1ЧНЧ1ГСНОИПХИЛ<|> Э Х1ЧНН8И IUIfN99d9U HWHfO КНШЭ|риОпНССЧ ек^о — I f KOHfolld

ГОСТ Р МЭК 821-2000

2.2 Линии шины пересылки данных

Линии шины пересылки данных подразделяются натри группы:

-линии адресации: Л01 — АЗ I (address lines 01—31),

АМО—АМ5 (address modifier lines 0—5),

DSO* (data strobe 0*).

DS Iе (data strobe 1*).

LWORD* (long word*);

- линии данных: DOO—D31 (data lines 00—31);

- линии управления: AS* (address strobe).

DSO*,

DS1*,

BERR* (bus error),

D EACK* (data acknowledge*), WRITE*.

Замечание 2.1. Два строба данных (DS0* и DS!*) выполняют двоякую функцию:

- их логические уровни используются для выбора байта (байтов), к которому (ым) осуществляется обращение;

- их перепады используются также в качестве синхросигналов для координирования пересылки данных между задатчиком и исполнителем.

2.2.1 Линии адресации

Наименьшей адресуемой единицей запоминающего устройства является байтовая ячейка. Каждой байтовой ячейке присваивается уникальный двоичный адрес. Каждая байтовая ячейка может быть отнесена к одной из четырех категорий в соответствии со значением двух младших разрядов ее адреса (см. таблицу 2.1).

Таблица 2.1 — Категории байтовых ячеек

Kate горим | Ларес байта |

БАЙТ (0) | хххххх.....ххххххоо |

БАЙТ(1) | ХХХХХХ.....ХХХХХХ01 |

БАЙТ (2) | ХХХХХХ.....ХХХХХХ 10 |

БАЙТ (3) | ХХХХХХ.....ХХХХХХ11 |

Набор байтовых ячеек, адреса которых различаются только двумя младшими разрядами, называется четырехбайтовой группой или группой БАЙТЫ (0—3). За один цикл шины пересылки данных можно одновременно обратиться к части или ко всем байтам четырехбайтовой группы.

Задатчики используют адресные линии А02—A3I для выбора четырехбайтовой группы, к которой будет происходить обращение. Четыре дополнительные линии (DST, DS0*, А01 и LWORD*), в свою очередь, выбирают, к какой байтовой ячейке (ячейкам) в пределах этой четырехбайтовой группы происходит обращение во время пересылки данных. Используя эти четыре линии, задатчик может обращаться к одной, двум, трем или четырем байтовым ячейкам одновременно, как показано в таблице 2.2.

Таблица 2.2 — Использование сигналов DSO*. DSI*, АО! и LWORD* для выбора байтовых ячеек

Выбираемые байтовые ячейки | DSC | DS0* | АО! | LWORD* |

Однобайтовый доступ БАЙТ (0) | Низкий | Высокий | Низкий | Высокий |

БАЙТ(1) | Высокий | Низкий | Низкий | Высокий |

БАЙТ (2) | Низкий | Высокий | Высокий | Высокий |

БАЙТ (3) | Высокий | Низкий | Высокий | Высокий |

12

Окончание таблицы 2.2

ГОСТ РМЭК 821-2000

Выбираемые байтовые ячейки | DSC | OSIf | Л01 | LWORD* |

Двухбайтовый доступ | ||||

Байты (0—1) низкий | Низкий | Низкий | Высокий | |

БАЙТЫ (1—2) низкий | Низкий | Высокий | Низкий | |

БАЙТЫ (2—3) низкий | Низкий | Высокий | Высокий | |

Трехбайтовый доступ | ||||

БАЙТЫ (0—2) низкий | Высокий | Низкий | Низкий | |

БАЙТЫ (1—3) высокий | Низкий | Низкий | Низкий | |

Четы рехба итоны й доступ | ||||

БАЙТЫ (0—3) низкий | Низкий | Низкий | Низкий |

Замечание 2.2. При установке обоих стробов данных низкими один строб данных может установиться низким несколько позднее другого. В этом случае уровни сигналов, указанные в таблице 2.2. подразумевают окончательно установившиеся уровни.

Замечание 2.3. Для данных уровней четырех сигнальных линий, указанных в таблице 2.2. возможны 16 комбинаций. Из этих 16 две комбинации являются запрещенными и не используются (см. правило 2.1).

Прочим 2.1. Задатчики НЕ ДОЛЖНЫ ФОРМИРОВАТЬ циклов шины пересылки данных в случаях, когда окончательные уровни сигналов DSO*. DSI*, АО/ и LWORD* составляют одну из следующих запрещенных комбинаций:

DS! * | DS0* | АО/ | LWORD* |

высокий | низкий | высокий | низкий |

низкий | высокий | высокий | низкий |

Разрешение 2.1. Когда задатчик обращается к байтовым ячейкам Ь\Й ГЫ (1—2) (см. таблицу 2.2). он МОЖЕТ сформировать на короткое время в виде переходных состояний одну из двух комбинаций, приведенных в правиле 2.1 (т.е. в то время, как один строб данных перейдет на низкий логический уровень, а другой на него не перейдет).

Замечание 2.4. Всякий раз, когда задатчик устанавливает LWORD* низким и Л01 высоким, он устанавливает оба строба данных низкими (любая другая комбинация является запрещенной). Проектировщики модулей могут воспользоваться этим обстоятельством .тля упрощения логической схемы исполнителей.

Разрешение 2.2. С целью упрощения требуемой схемы исполнители, отвечающие на какие-либо никлы, в которых происходит обращение к байтовым ячейкам БАЙТЫ (1—2) (см. таблицу 2.2), МОГУТ быть спроектированы без логики, отличающей эти циклы от двух запрещенных циклов, указанных в правиле 2.1.

2.2.2 J1 инии модификатора адреса

Имеется шесть линий модификатора адреса. Они позволяют задатчику отправлять дополнительную двоичную информацию исполнителю во время циклов шины пересылки данных. В таблице 2.3 указаны все 64 возможных кода модификатора адреса, которые подразделены на три класса.

а) Определяемые стандартом, которые включают:

- коды модификатора адреса короткой адресации, указывающие, что для выбора группы БЛИТЫ (0—3) используются адресные линии Л02—А15;

- колы модификатора адреса стандартной адресации, указывающие, что для выбора группы БАЙТЫ (0—3) используются адресные линии А02—А23;

- колы модификатора адреса расширенной адресации, указывающие, что для выбора группы БАЙТЫ (0—3) используются адресные линии Л02—Л31.

б) Зарезервированные коды.

в) Коды, определяемые пользователем.

ГОСТ Р МЭК 821-2000

Таблица 2.3 — Коды модификатора адреса

Шсстказ-цатсрич-НЫЙ код | Линии модификатора | Функция | |||||

5 | 4 | адреса | |||||

3 | J | 1 | 0 | ||||

3F | н | II | Н | 11 | Н | Н | Стандартная супсрвизорная блочная пересылка |

ЗЕ | 11 | II | II | II | II | L | Стандартный супервизорный доступ к программе |

3D | н | II | н | II | L | II | Стандартный супервизорный доступ к данным |

ЗС | 11 | II | и | II | L | L | Зарезервирован |

ЗВ | н | II | II | L | Н | II | Стандартная непривилегированная блочная пересылка |

ЗА | 11 | II | н | L | II | L | Стандартный непривилегированный доступ к программе |

39 | 11 | II | и | L | L | II | Стандартный непривилегированный доступ к данным |

38 | 11 | II | н | L | L | L | Зарезервирован |

37 | 11 | II | L | II | Н | II | Зарезервирован |

36 | н | II | L | II | II | L | Зарезервирован |

35 | 11 | II | L | II | L | II | Зарезервирован |

34 | 11 | II | L | II | L | L | Зарезервирован |

33 | 11 | II | L | L | Н | II | Зарезервирован |

32 | 11 | II | L | L | И | L | Зарезервирован |

31 | 11 | II | L | L | L | II | Зарезервирован |

30 | 11 | II | L | L | L | L | Зарезервирован |

2F | 11 | L | Н | II | Н | II | Зарезервирован |

2Е | 11 | L | И | II | И | L | Зарезервирован |

2D | 11 | L | н | II | L | II | Короткий супервизорный доступ |

2С | 11 | L | и | II | L | L | Зарезервирован |

2В | 11 | L | н | L | И | II | Зарезервирован |

2А | 11 | L | и | L | И | L | Зарезервирован |

29 | 11 | L | н | L | L | II | Короткий непривилегированный доступ |

28 | 11 | L | и | L | L | L | Зарезервирован |

27 | 11 | L | L | II | II | II | Зарезервирован |

26 | 11 | L | L | II | И | L | Зарезервирован |

25 | 11 | L | L | II | L | II | Зарезервирован |

24 | 11 | L | L | II | L | L | Зарезервирован |

23 | 11 | L | L | L | Н | II | Зарезервирован |

22 | 11 | L | L | L | Н | L | Зарезервирован |

21 | 11 | L | L | L | L | II | Зарезервирован |

20 | 11 | L | L | L | L | L | Зарезервирован |

1F | L | 11 | II | II | Н | II | Зарезервирован |

1Е | L | II | II | II | И | L | Определяемая пользователем |

1D | L | II | Н | II | L | II | Определяемая пользователем |

1С | L | II | Н | II | L | L | Определяемая пользователем |

1В | L | II | н | L | и | II | Определяемая пользователем |

1А | L | II | н | L | н | L | Определяемая пользователем |

19 | L | II | н | L | L | II | Определяемая пользователем |

18 | L | II | н | L | L | L | Определяемая пользователем |

17 | L | II | L | II | и | II | Определяемая пользователем |

16 | L | II | L | II | н | L | Определяемая пользователем |

15 | L | II | L | II | L | II | 011 ре дел яе мая пол ь зова г еле м |

14 | L | II | L | II | L | L | Определяемая пользователем |

13 | L | II | L | L | Н | II | Определяемая пользователем |

12 | L | II | L | L | н | L | Определяемая пользователем |

11 | L | II | L | L | L | II | Определяемая пользователем |

10 | L | II | L | L | L | L | Определяемая пользователем |

0F | L | L | Н | Н | Н | Н | Расширенная супервизорная блочная пересылка |

0Е | L | L | Н | II | И | L | Расширенный супервизорный доступ к программе |

0D | L | L | II | II | L | II | Расширенный супервизорный доступ к данным |

ОС | L | L | II | II | L | L | Зарезервирован |

ОВ | L | L | н | L | Н | II | Расширенная непривилегированная блочная пересылка |

0А | L | L | II | L | И | L | Расширенный непривилегированный доступ к программе |

09 | L | L | н | L | L | II | Расширенный непривилегированный доступ к данным |

14

Окончание таблицы 2.3

ГОСТ РМЭК 821-2000

Шестнадцатеричный коа | Липни модификатора адреса 5 4 3 2 10 | Функция |

08 07 06 05 0* 03 02 01 00 | L L Н L L L L L L П Н Н L L L Н П L L L L П L Н L L L Н L L L L L L Н II L L L L Н L L L L L L Н L L L L L L | Зарезервирован Зарезервирован Зарезервирован Зарезервирован Зарезервирован Зарезервирован Зарезервирован Зарезервирован Зарезервирован |

L — низкий логический уровень сигнала; И — высокий логический уровень сигнала. | ||

Привило 2.2. Коды, указанные в таблице 2.3. за исключением кодон, определяемых пользователем, НЕ ДОЛЖНЫ ИСПОЛЬЗОВА ТЬСЯ в иных целях, чем это указанно.

Правило 2.3. Исполнители НЕ ДОЛЖНЫ О ТВЕЧА ТЬ на зарезервированные коды модификатора адреса.

Замечание 2.5. Зарезервированные коды адресного модификатора предназначены для расширения в будущем функциональных возможностей системы. Если исполнители отвечают на такие коды, это может привести к их несовместимости с тем их конкретным использованием, которое будет определено позднее.

Разрешение 2.3. Коды, определяемые пользователем. МОГУТ использоваться для любых целей, которые сочтут нужными фирмы-изготовители и пользователи модулей (переключение страниц памяти, защита памяти, идентификация задатчика или задачи, привилегированный доступ к ресурсам и тд.).

Рекомендация 2.1. Чтобы позволить пользователям приспособить для своих нужд определяемые ими коды модификатора адреса, необходимо дешифровать их удобным способом в модулях исполнителей. Далее пользователи могут конфигурировать модуль, выполняя любое декодирование, которое необходимо их системе.

Замечание 2.6. Удобным средством декодирования колов модификатора адреса являются устанавливаемые в панельки на плату программируемые устройства.

Предложение 2.1. В тех случаях, когда исполнители содержат программируемые элементы (например. ППЗУ или ПЛМ). устанавливаемые в панельки на платы, предлагается эти элементы программировать так. чтобы указанные типы исполнителей отвечали на следующие коды модификатора адреса:

исполнители А16 (address lines AOI—AI5) с функцией

D08(O) (data lines 00-07. odd),

D08(EO) (data lines D(W D07/DDS -D15 even/odd),

DI6 (data lines DOO—DI5) или

D32 (data lines D00-D3I): 29. 2D;

исполнители A24 (address lines AOI—A23) с функцией

D08(O), DOSt EO).

D16 или D32 : 39, ЗА, 3D и ЗЕ;

исполнители А32 (address lines AOI—A3I) с функцией

D08(O). DOS(EO),

D16 или D32 : 09. 0A, 0D и OE;

исполнители Л24 с функцией BLT (block transfer): ЗВ. 3F;

исполнители A32 с функцией BLT : OB. OF.

Мнемонические обозначения AI6, А24 и А32 определены в таблице 2.9. a D08(O). DOS(EO). DI6. D32 и BLT - в таблицах 2.10 и 2.11.

15

ГОСТ Р МЭК 821-2000

2.2.3 Л и и ни да и и ы х

Системы можно построить с двумя конфигурациями объединительной платы; первая обладает 16 линиями данных (DOO—DI5), вторая - 32 линиями данных (DOO D31). Конфигурация объединительной платы, имеющей 16 линий данных, позволяет задатчику обращаться одновременно только к двум байтовым ячейкам, тогда как объединительная плата с 32 линиями данных позволяет задатчику одновременно обращаться к четырем байтовым ячейкам. Когда задатчик выбрал одну, две. три или четыре байтовые ячейки в соответствии с методом, приведенным в 2.2.1. он может пересылать данные между собой и этими ячейками по линиям данных. Таблица 2.4 показывает, как используются линии данных для доступа к байтовым ячейкам.

Таблица 2.4 — Использование линии данных для доступа к байтовым ячейкам

Доступ к байтовым ячейкам | D24-D31 | DI6-D23 | D08-DI5 | D00-D07 |

БАЙТ (0) | БАЙТ (0) | |||

БАЙТ (1) | БАЙТ (1) | |||

БАЙТ (2) | БАЙТ (2) | |||

БАЙТ (3) | БАЙТ (3) | |||

БАЙТЫ (0-1) | БАЙТ (0) | БАЙТ (1) | ||

БАЙТЫ (1-2) | БАЙТ (1) | БАЙТ (2) | ||

БАЙТЫ (2-3) | БАЙТ (2) | БАЙТ (3) | ||

БАЙТЫ (0-2) | БАЙТ (0) | БАЙТ (1) | БАЙТ (2) | |

БАЙТЫ (1-3) | БАЙТ (1) | БАЙТ (2) | БАЙТ (3) | |

БАЙТЫ (0-3) | БАЙТ (0) | БАЙТ(1) | БАЙТ (2) | БАЙТ (3) |

2.2.4 Л и нии у п р а в л е и и я тины пересылки да н н ы х

Для управления пересылкой данных по шине используются следующие сигнальные линии:

AS* — линия адресного строба (далее — линия AS*)

DSO* — линия строба данных ноль (далее — линия DS0*)

DS1* — линия строба данных один (далее — линия DSI*)

BERR* — линия сигнала ошибки магистрали (далее — линия BERR*)

DTACK* - линия сигнала подтверждения пересылки данных (далее — линия DTACK*)

WRITE* — линия сигнала считывания/записи (далее — линия WRITE*)

2.2.4.1 Линия AS*

Отрицательный перепад сигнала на линии AS* информирует всех исполнителей, что адрес стабилен и может быть принят.

2.2.4.2 Линии DS0* и DSI*

Кроме своих функций выбора байтовых ячеек для пересылки данных, как это описано в 2.2.1, стробы данных выполняют также дополнительные функции. При циклах записи первый отрицательный перепад строба данных указывает, что задатчик поместил на шину данных достоверные данные. При циклах считывания первый положительный перепад сообщает исполнителю, что тот может снять свои данные с шины данных.

Замечание 2.7. Как указано в 2.6, задатчикам не разрешается устанавливать низким ни тот, ни другой строб данных до установки низким AS*. Однако из-за того обстоятельства, что линия AS* может быть загружена на объединительной плате значительно больше, чем линии стробов данных. исполнители и адресные мониторы могут обнаружить отрицательный перепад на линиях стробов данных до того, как они обнаружат отрицательный перепад на линии AS*.

Разрешение 2.5. Исполнители, не имеющие функциональной возможности блочной пересылки (см. 2.3.7). и адресные мониторы МОГУТ быть спроектированы для захвата адреса, когда они обнаруживают отрицательный перепад на любой линии строба данных, а не по отрицательному' перепаду AS*.

16

ГОСТ РМЭК 821-2000

Замечание 2.8. Исполнителям и адресным мониторам, которые захватывают адрес по отрицательному перепаду строба (стробов) данных, нет необходимост и контролировать линию AS*.

Замечание 2.9. Чтобы полностью воспользоваться преимуществами конвейерной адресации (см. 2.4.2) или выполнять циклы блочного считывания и записи, исполнителю следует захватывать адрес по отрицательному перепаду AS*.

2.2.4.3 Линия DTACK*

Исполнитель устанавливает DTACK* низким, чтобы показать, что он успешно принял данные в цикле записи. В цикле считывания исполнитель устанавливает DTACK* низким, чтобы показать, что он поместил данные налипни данных.

2.2.4.4 Линия BERR*

BERR* устанавливается исполнителем или шинным таймером низким, чтобы показать задатчику, что пересылка данных оказалась безуспешной. Например, если задатчик пытается осуществить запись в ячейку ПЗУ. отвечающий исполнитель может установить BERR* низким. Если задатчик пытается осуществить обращение к ячейке, которая не предоставлена ни одним из исполнителей, то после какого-то заданного временного интервала (тайм-аута) шинный таймер устанавливает BERR* низким.

Предложение 2.2. Предлагается проектировать исполнители так. чтобы они отвечали отрицательным перепадом на линии BERR* при обнаружении неисправимой ошибки в данных, которые они выбирают из своего внутреннего запоминающего устройства во время цикла считывания.

2.2.4.5 Линия WRITE*

Для сигнала на линии WRITE4, который стробируется отрицательным перепадом первого поступающего строба данных, главное значение имеет его логический уровень. Он используется задатчиком, чтобы показать направление операций пересылки данных. Если W RITE* устанавливается низким, направление пересылки данных — от задатчика к исполнителю. Если W RITE* устанавливается высоким, направление пересылки данных — от исполнителя к задатчику.

2.3 Функциональные блоки шины пересылки данных